Topic3:Verification and Test Verilog for Testbench 。Testbench anatomy Behavioral modeling for Testbench 。Some examples Timing specification 。Delay model 。Timing verification 。Pipeline technology Design For Test(DFT) Test vs.Verification Build In Self Test (BIST) Scan and Boundary Scan 2021/1/13 ASIC Design,by Yan Bo 8

ASIC Design, by Yan Bo Topic3: Verification and Test Verilog for Testbench • Testbench anatomy • Behavioral modeling for Testbench • Some examples Timing specification • Delay model • Timing verification • Pipeline technology Design For Test (DFT) Test vs. Verification Build In Self Test (BIST) Scan and Boundary Scan 2021/1/13 8

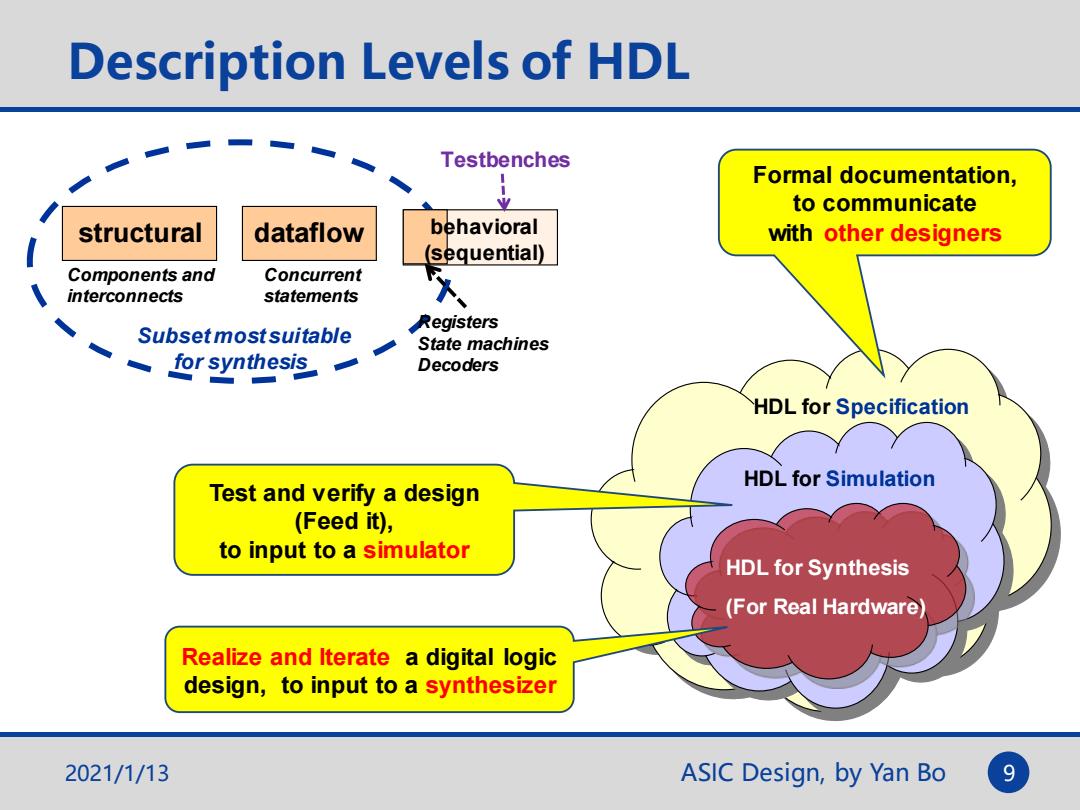

Description Levels of HDL Testbenches Formal documentation, 业 to communicate structural dataflow behavioral with other designers (sequential) Components and Concurrent interconnects statements 水 Subsetmostsuitable Registers State machines for synthesis一 Decoders HDL for Specification HDL for Simulation Test and verify a design (Feed it), to input to a simulator HDL for Synthesis (For Real Hardware) Realize and Iterate a digital logic design,to input to a synthesizer 2021/1/13 ASIC Design,by Yan Bo

ASIC Design, by Yan Bo 9 Description Levels of HDL HDL for Specification HDL for Simulation HDL for Synthesis (For Real Hardware) Formal documentation, to communicate with other designers Test and verify a design (Feed it), to input to a simulator Realize and Iterate a digital logic design, to input to a synthesizer 2021/1/13 Components and interconnects structural behavioral (sequential) Registers State machines Decoders Subset most suitable for synthesis Testbenches dataflow Concurrent statements

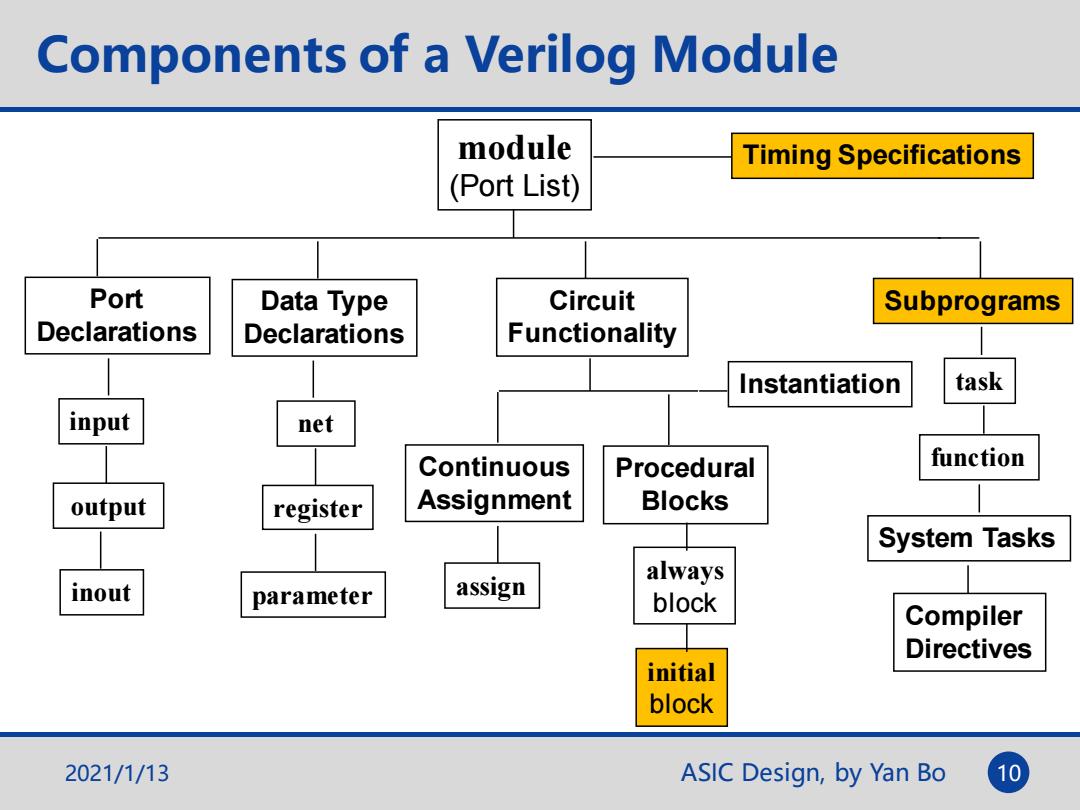

Components of a Verilog Module module Timing Specifications (Port List) Port Data Type Circuit Subprograms Declarations Declarations Functionality Instantiation task input net Continuous Procedural function output register Assignment Blocks System Tasks always inout parameter assign block Compiler Directives initial block 2021/1/13 ASIC Design,by Yan Bo 10

ASIC Design, by Yan Bo Components of a Verilog Module module (Port List) Port Declarations input output inout Data Type Declarations net register parameter Circuit Functionality Timing Specifications Continuous Assignment assign Procedural Blocks always block Subprograms task function System Tasks Compiler Directives Instantiation initial block 2021/1/13 10

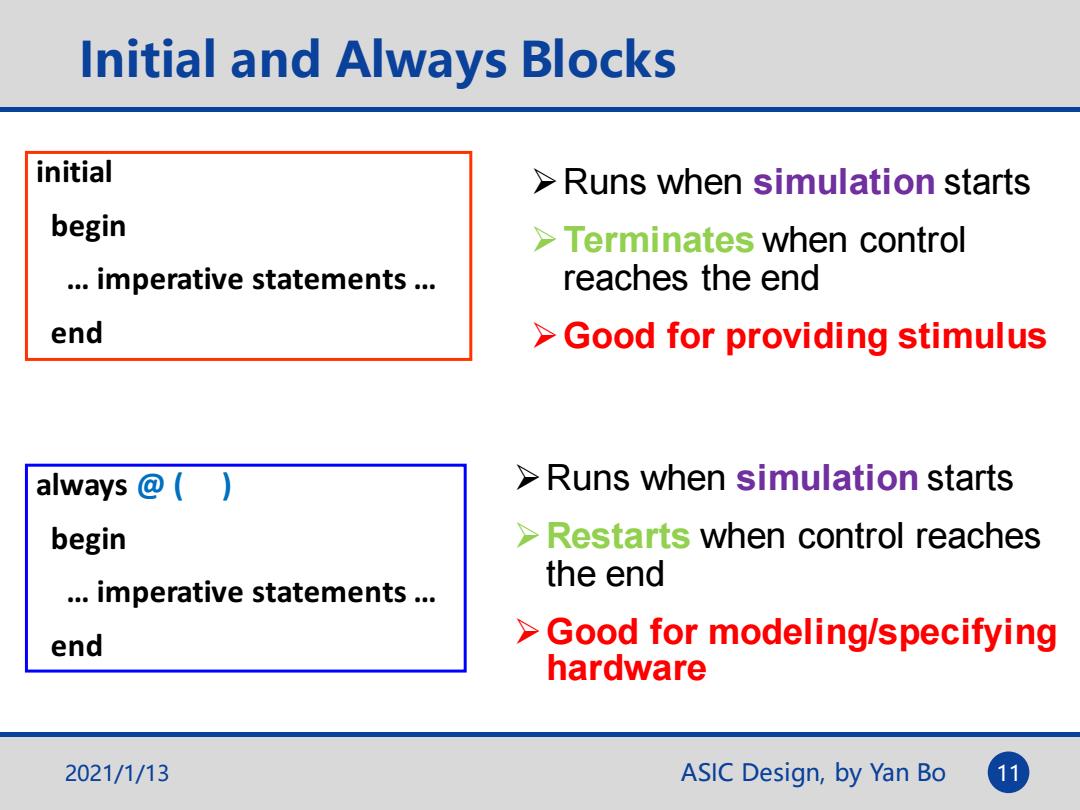

Initial and Always Blocks initial Runs when simulation starts begin >Terminates when control ..imperative statements... reaches the end end >Good for providing stimulus always Runs when simulation starts begin Restarts when control reaches ..imperative statements... the end end > Good for modeling/specifying hardware 2021/1/13 ASIC Design,by Yan Bo 11

ASIC Design, by Yan Bo Initial and Always Blocks initial begin … imperative statements … end always @ ( ) begin … imperative statements … end ➢Runs when simulation starts ➢Terminates when control reaches the end ➢Good for providing stimulus ➢Runs when simulation starts ➢Restarts when control reaches the end ➢Good for modeling/specifying hardware 2021/1/13 11

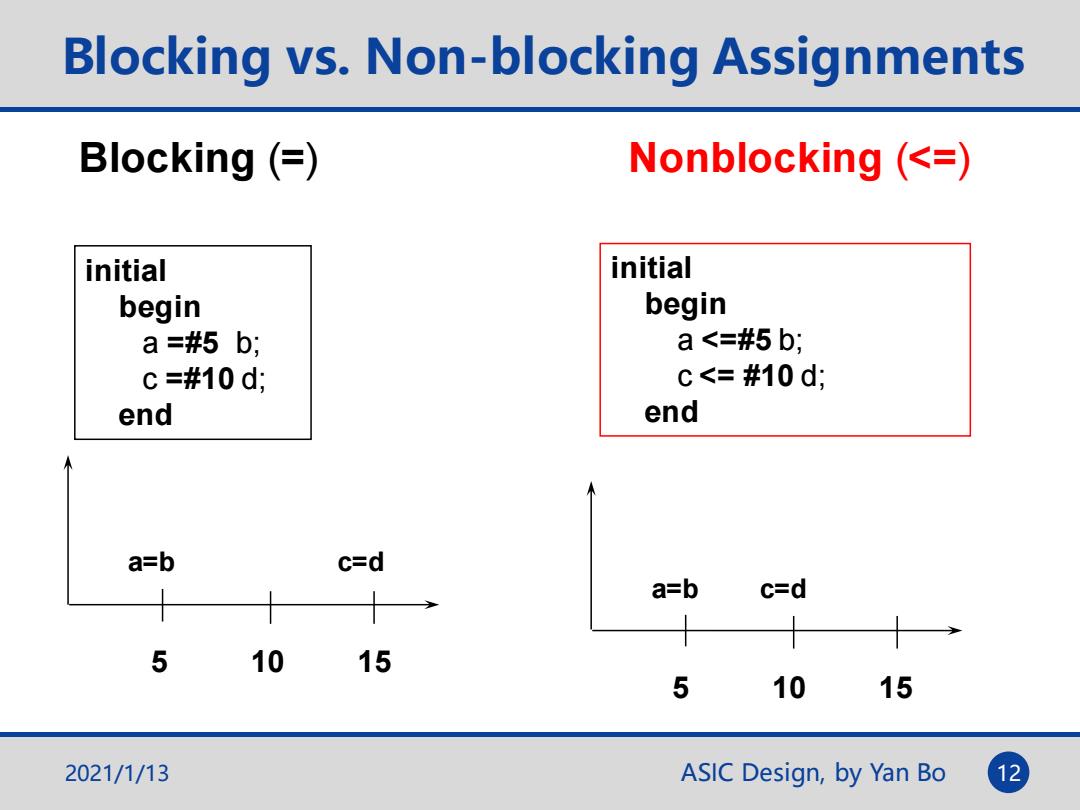

Blocking vs.Non-blocking Assignments Blocking (= Nonblocking (<= initial initial begin begin a=#5b; a<=#5b; c=#10d; C<=#10d; end end a=b c=d a=b c=d 5 10 15 5 10 15 2021/1/13 ASIC Design,by Yan Bo 12

ASIC Design, by Yan Bo Blocking vs. Non-blocking Assignments Blocking (=) Nonblocking (<=) initial begin a =#5 b; c =#10 d; end initial begin a <=#5 b; c <= #10 d; end 5 10 15 a=b c=d 5 10 15 a=b c=d 2021/1/13 12