第八节 组合逻辑电路中的竞争冒险 一、竞争冒险现象及其产生原因 1.竞争冒险现象 前面分析设计组合电路时,都是在信号稳态情况 下讨论的,实际电路工作时,信号变化需要时间, 门电路对信号也产生一定的延时,而各个门的延 时不尽相同,因此若干个彼此独立的输入信号就 不可能恰好同时变化,即使同一信号经过不同的 通路到达某个门的输入端也会有先有后,于是产 生时差,这种现象称为竞争

第八节 组合逻辑电路中的竞争冒险 一、竞争冒险现象及其产生原因 1.竞争冒险现象 前面分析设计组合电路时,都是在信号稳态情况 下讨论的,实际电路工作时,信号变化需要时间, 门电路对信号也产生一定的延时,而各个门的延 时不尽相同,因此若干个彼此独立的输入信号就 不可能恰好同时变化,即使同一信号经过不同的 通路到达某个门的输入端也会有先有后,于是产 生时差,这种现象称为竞争

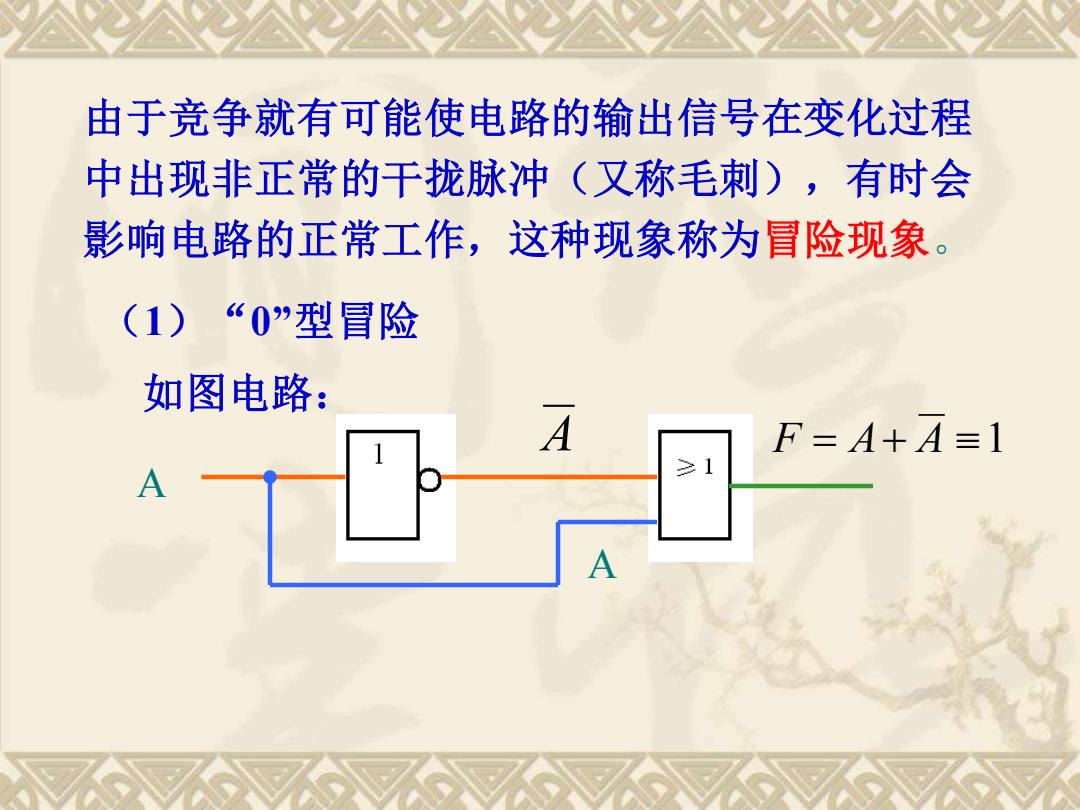

由于竞争就有可能使电路的输出信号在变化过程 中出现非正常的干拢脉冲(又称毛刺),有时会 影响电路的正常工作,这种现象称为冒险现象。 (1)“0”型冒险 如图电路: A F=4+4=1 ≥1 A

由于竞争就有可能使电路的输出信号在变化过程 中出现非正常的干拢脉冲(又称毛刺),有时会 影响电路的正常工作,这种现象称为冒险现象。 如图电路: A A A F = A+ A 1 (1)“0”型冒险

A A A+A 0 由于存在门延迟,但由于出现负尖脉峰,在脉峰 期间不满足F=A+A=1 称为“0”型冒险

A A A+A “1” “0” tpd 由于存在门延迟,但由于出现负尖脉峰,在脉峰 期间不满足 称为“0”型冒险。 F = A+ A 1

(2)“1”型冒险 如图所示电路: A F=AA=0 A & A A A4=0 “0

如图所示电路: (2)“1”型冒险 A A A F = AA 0 A A AA = 0 “1” “0

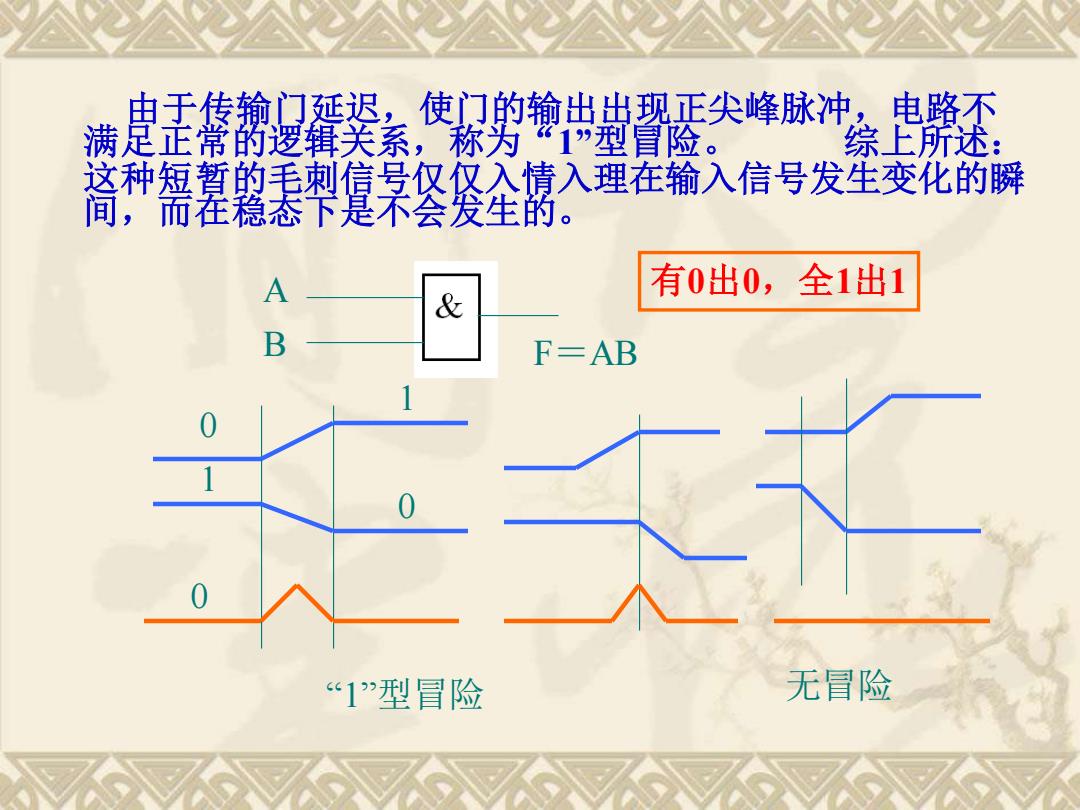

由于传输门延迟,使门的输出出现正尖峰脉冲,电路不 满定正常的逻辑关系,称为“”型會险。 综上所述: 这种短暂的毛刺信号仅仅入情入理在输入信号发生变化的瞬 间,而茬稳态下是不会发生的。 A 有0出0,全1出1 & B F=AB “1”型冒险 无冒险

由于传输门延迟,使门的输出出现正尖峰脉冲,电路不 满足正常的逻辑关系,称为“1”型冒险。 综上所述: 这种短暂的毛刺信号仅仅入情入理在输入信号发生变化的瞬 间,而在稳态下是不会发生的。 A 有0出0,全1出1 B F=AB 0 1 0 1 0 “1”型冒险 无冒险