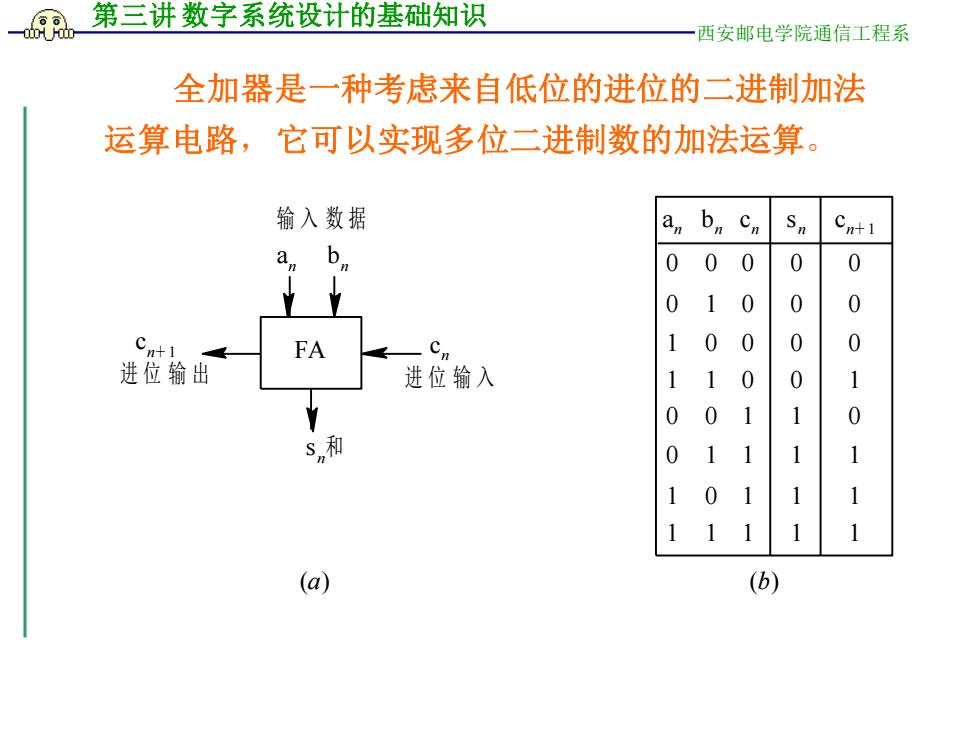

第三讲数字系统设计的基础知识 西安邮电学院通信工程系 全加器是一种考虑来自低位的进位的二进制加法 运算电路,它可以实现多位二进制数的加法运算。 输入数据 an Cn+1 a, 0 0 0 0 0 0 1 0 Cn+l FA Cn 1 0 0 0 0 进位输出 进位输入 1 1 0 0 1 0 0 1 0 ,和 0 1 1 1 1 1 01 1 1 111 1 1 (a) (b)

第三讲 数字系统设计的基础知识 西安邮电学院通信工程系 全加器是一种考虑来自低位的进位的二进制加法 运算电路,它可以实现多位二进制数的加法运算。 FA 输 入 数 据 an bn s n 和 cn+1 进 位 输 出 0 0 0 1 1 0 1 1 0 0 0 0 (a) (b) an bn s n cn+1 0 0 0 1 cn 进 位 输 入 0 0 0 1 1 0 1 1 1 1 1 1 0 1 1 1 0 0 0 0 cn 1 1 1 1

第三讲数字系统设计的基础知识 西安邮电学院通信工程系 Verilog的功能描述 module adder4(cout,sum,ina,inb,cin); output [3:0]sum; output cout; 组合运 算符 input [3:0]ina,inb; input cin; 组合逻辑的verilog描 assign{cout,sum}=ina+inbtc述方法小结: endmodule 用assign赋值语句。 用电平敏感的always 语句

第三讲 数字系统设计的基础知识 西安邮电学院通信工程系 Verilog的功能描述 module adder4(cout,sum,ina,inb,cin); output[3:0] sum; output cout; input[3:0] ina,inb; input cin; assign {cout,sum}=ina+inb+cin; endmodule 组合运 算符 组合逻辑的verilog描 述方法小结: ❖用assign赋值语句。 ❖用电平敏感的always 语句

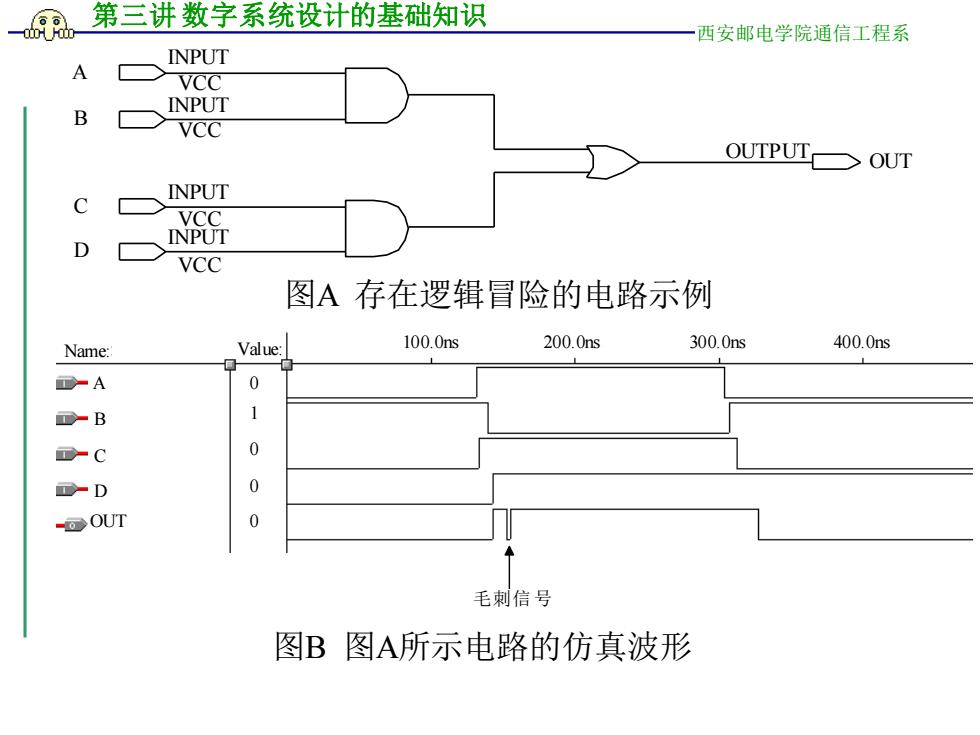

第三讲数字系统设计的基础知识 西安邮电学院通信工程系 组合逻辑电路的竞争与冒险 。信号在通过连线和逻辑单元时都有一定的延时。延时的大小与连 线的长短和逻辑单元的数目有关,同时还受器件的制造工艺、工 作电压、温度等条件的影响。不同延时产生逻辑竞争现象。 ~由于存在竞争,在组合逻辑输入信号变化时,组合逻辑的输出稳 定前往往会出现一些“毛刺”。如果一个组合逻辑电路中有“毛 刺”出现,就称该电路存在“冒险”。 图A给出了一个逻辑冒险的例子,从图B的仿真波形可以看出, “A、B、C、D"四个输入信号的高低电平变换不是同时发生的, 导致输出信号“0UT"出现了毛刺。 冬判断一个逻辑电路是否会产生冒险, 可以用逻辑函数的卡诺图或 逻辑函数表达式来进行判断。具体可参考有关数字电路方面的书 籍

第三讲 数字系统设计的基础知识 西安邮电学院通信工程系 组合逻辑电路的竞争与冒险 ❖ 信号在通过连线和逻辑单元时都有一定的延时。 延时的大小与连 线的长短和逻辑单元的数目有关, 同时还受器件的制造工艺、工 作电压、 温度等条件的影响。不同延时产生逻辑竞争现象。 ❖ 由于存在竞争,在组合逻辑输入信号变化时, 组合逻辑的输出稳 定前往往会出现一些“毛刺”。如果一个组合逻辑电路中有“毛 刺”出现,就称该电路存在“冒险”。 ❖ 图A 给出了一个逻辑冒险的例子, 从图B的仿真波形可以看出, “A、 B、 C、 D”四个输入信号的高低电平变换不是同时发生的, 导致输出信号“OUT”出现了毛刺。 ❖ 判断一个逻辑电路是否会产生冒险, 可以用逻辑函数的卡诺图或 逻辑函数表达式来进行判断。 具体可参考有关数字电路方面的书 籍

6 第三讲数字系统设计的基础知识 西安邮电学院通信工程系 INPUT A VCC INPUT B VCC OUTPUT OUT INPUT C VCC INPUT D VCC 图A存在逻辑冒险的电路示例 Name: Value: 100.0ns 200.0ns 300.0ns 400.0ns DA 0 B 1 工-C 0 D 0 OUT 0 毛刺信号 图B图A所示电路的仿真波形

第三讲 数字系统设计的基础知识 西安邮电学院通信工程系 图A 存在逻辑冒险的电路示例 A B C D INPUT INPUT VCC VCC INPUT INPUT VCC VCC OUT OUTPUT 毛刺信号 0 1 0 0 0 Name: A B C D OUT Value: 100.0ns 200.0ns 300.0ns 400.0ns 图B 图A所示电路的仿真波形

第三讲数字系统设计的基础知识 西安邮电学院通信工程系 消除逻辑冒险的影响 冬数字电路设计中,采用格雷码计数器、冗余电路等, 可以大大减少毛刺,但它并不能完全消除毛刺。 消除毛刺信号通常使用“采样”的方法。一般毛刺出 现在信号发生电平转换的时刻,而在信号稳定后是不 会有毛刺的。如果在信号稳定后对其进行“采样”, 就可以消除毛刺信号的影响。 冬方法一是在信号的稳定时间内,用一定宽度的高电平 脉冲与信号做逻辑“与”运算,由此获取消除毛刺的 输出信号。方法二是利用D触发器的D输入端对毛刺信 号不敏感的特点,在输出信号的保持时间内,用触发 器读取组合逻辑的输出信号

第三讲 数字系统设计的基础知识 西安邮电学院通信工程系 消除逻辑冒险的影响 ❖ 数字电路设计中, 采用格雷码计数器、 冗余电路等, 可以大大减少毛刺, 但它并不能完全消除毛刺。 ❖ 消除毛刺信号通常使用“采样”的方法。一般毛刺出 现在信号发生电平转换的时刻,而在信号稳定后是不 会有毛刺的。 如果在信号稳定后对其进行“采样” , 就可以消除毛刺信号的影响。 ❖ 方法一是在信号的稳定时间内, 用一定宽度的高电平 脉冲与信号做逻辑“与”运算, 由此获取消除毛刺的 输出信号。方法二是利用D触发器的D输入端对毛刺信 号不敏感的特点, 在输出信号的保持时间内, 用触发 器读取组合逻辑的输出信号