第五讲数字系统设计的实现与验证 西安邮电学院通信工程系 第五讲数字系统设计的实现与验证 什么是逻辑综合 Verilog HDL的综合要求 逻辑综合流程、工艺库和设计约束 基于quartus2的逻辑综合与实现 冬静态时序分析验证 冬辅助设计工具简介 冬动态时序仿真验证 编程与配置

第五讲 数字系统设计的实现与验证 西安邮电学院通信工程系 第五讲 数字系统设计的实现与验证 ❖ 什么是逻辑综合 ❖ Verilog HDL的综合要求 ❖ 逻辑综合流程、工艺库和设计约束 ❖ 基于quartus2的逻辑综合与实现 ❖ 静态时序分析验证 ❖ 辅助设计工具简介 ❖ 动态时序仿真验证 ❖ 编程与配置

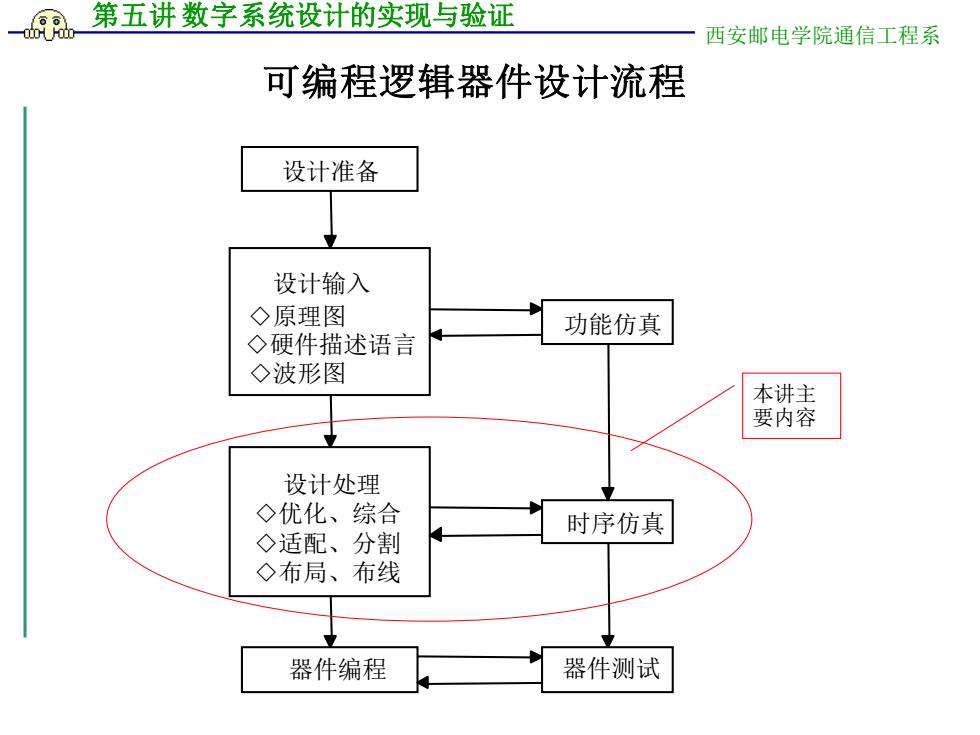

第五讲数字系统设计的实现与验证 西安邮电学院通信工程系 可编程逻辑器件设计流程 设计准备 设计输入 ◇原理图 功能仿真 ◇硬件描述语言 ◇波形图 本讲主 要内容 设计处理 ◇优化、综合 时序仿真 ◇适配、分割 ◇布局、布线 器件编程 器件测试

第五讲 数字系统设计的实现与验证 西安邮电学院通信工程系 可编程逻辑器件设计流程 设计准备 设计输入 ◇原理图 ◇硬件描述语言 ◇波形图 设计处理 ◇优化、综合 ◇适配、分割 ◇布局、布线 器件编程 器件测试 时序仿真 功能仿真 本讲主 要内容

第五讲数字系统设计的实现与验证 西安邮电学院通信工程系 什么是逻辑综合 ?逻辑综合是在标准单元库(工艺库)和特定设计约束 的基础上,把设计的高层次描述转换成优化的门级网 表的过程。计算机辅助逻辑综合过程如下: HDL描述 设计约束 工艺库 转换 优化 映射 引擎 引擎 引擎 2级逻辑功能 优化后逻辑 工艺实现网表

第五讲 数字系统设计的实现与验证 西安邮电学院通信工程系 什么是逻辑综合 ❖ 逻辑综合是在标准单元库(工艺库)和特定设计约束 的基础上,把设计的高层次描述转换成优化的门级网 表的过程。计算机辅助逻辑综合过程如下: HDL描述 转换 引擎 2级逻辑功能 优化后逻辑 工艺实现网表 工艺库 优化 引擎 映射 引擎 设计约束

第五讲数字系统设计的实现与验证 西安邮电学院通信工程系 人工的逻辑综合过程 逻辑综合曾经是数字系 高层次描述 统设计中最复杂的过程。在 设计约束 人工逻辑综合设计时代,设 设计者的思想 计者首先理解高层次描述, 工艺库 然后考虑设计的时序、实现 面积、可测性和功耗等设计 门级表示 约束,最后用工艺库中的器 件作为基本单元,画出实现 是否符合 高层次描述的逻辑电路图, 设计要求? 并反复优化电路,达到设计 人 综合 约束的要求。这一过程实际 优化的门级表示 上是将人的大脑作为逻辑综 合工具

第五讲 数字系统设计的实现与验证 西安邮电学院通信工程系 人工的逻辑综合过程 逻辑综合曾经是数字系 统设计中最复杂的过程。在 人工逻辑综合设计时代,设 计者首先理解高层次描述, 然后考虑设计的时序、实现 面积、可测性和功耗等设计 约束,最后用工艺库中的器 件作为基本单元,画出实现 高层次描述的逻辑电路图, 并反复优化电路,达到设计 约束的要求。这一过程实际 上是将人的大脑作为逻辑综 合工具。 高层次描述 设计者的思想 门级表示 优化的门级表示 设计约束 工艺库 是否符合 设计要求? 人工 综合 否

第五讲数字系统设计的实现与验证 西安邮电学院通信工程系 自动逻辑综合工具的意义 自动逻辑综合工具带来了数字设计行业的革命,是现代 数字系统设计的基础。 手工设计问题: 自动逻辑综合工具设计特点: 冬设计时间长,对大规模设计容易 采用高层次描述,大规模电路设计 出错,甚至不可能完成。 容易,人为错误较少。 设计者不容易确定设计约束是否 ?无需过多关注设计约束,逻辑综合 满足。 工具将确保满足所有的约束。 设计优化困难,特别是系统级优 ~从高层次描述到逻辑门的转换非常 化。 快,且可得到全局优化的电路。人 工耗费数月的设计,现在可能仅需 。 在最终门级设计中发现设计错误, 数小时。 可能导致重新设计数千门电路。 冬模块重新设计所需时间更短,因设 设计与具体工艺库相关,不可重 计者只需修改RTL级设计。 用。 改变工艺库,设计可重用于不同工 艺

第五讲 数字系统设计的实现与验证 西安邮电学院通信工程系 自动逻辑综合工具的意义 手工设计问题: ❖ 设计时间长,对大规模设计容易 出错,甚至不可能完成。 ❖ 设计者不容易确定设计约束是否 满足。 ❖ 设计优化困难,特别是系统级优 化。 ❖ 在最终门级设计中发现设计错误, 可能导致重新设计数千门电路。 ❖ 设计与具体工艺库相关,不可重 用。 自动逻辑综合工具带来了数字设计行业的革命,是现代 数字系统设计的基础。 自动逻辑综合工具设计特点: ❖采用高层次描述,大规模电路设计 容易,人为错误较少。 ❖无需过多关注设计约束,逻辑综合 工具将确保满足所有的约束。 ❖从高层次描述到逻辑门的转换非常 快,且可得到全局优化的电路。人 工耗费数月的设计,现在可能仅需 数小时。 ❖模块重新设计所需时间更短,因设 计者只需修改RTL级设计。 ❖改变工艺库,设计可重用于不同工 艺