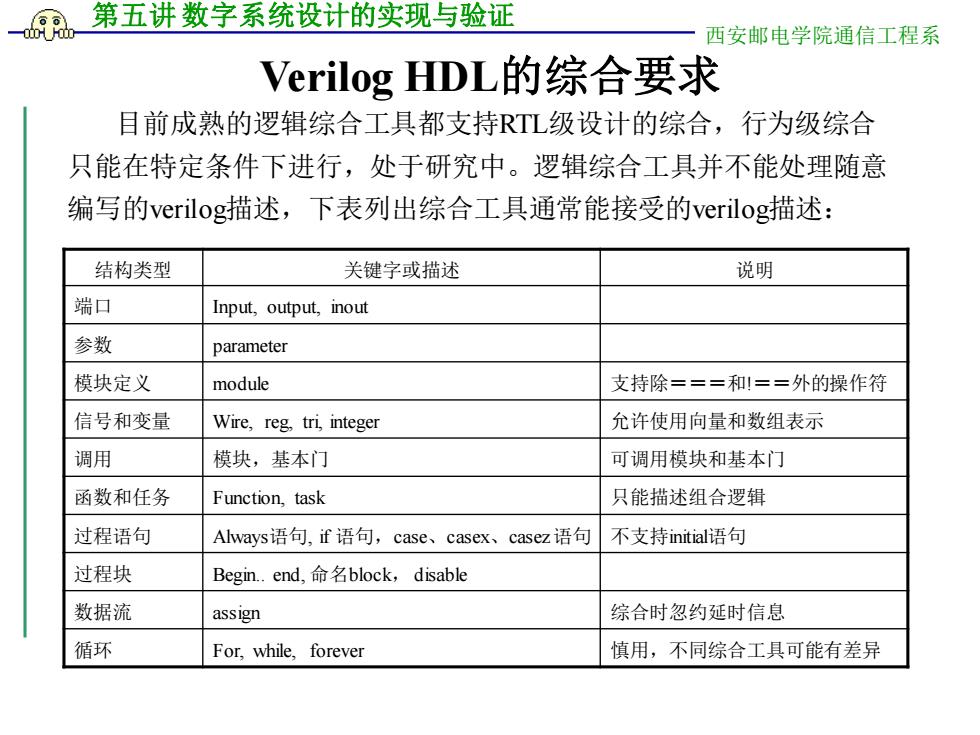

第五讲数字系统设计的实现与验证 西安邮电学院通信工程系 Verilog HDL的综合要求 目前成熟的逻辑综合工具都支持RTL级设计的综合,行为级综合 只能在特定条件下进行,处于研究中。逻辑综合工具并不能处理随意 编写的verilog描述,下表列出综合工具通常能接受的verilog描述: 结构类型 关键字或描述 说明 端口 Input,output,inout 参数 parameter 模块定义 module 支持除===和!==外的操作符 信号和变量 Wire,reg,tri,integer 允许使用向量和数组表示 调用 模块,基本门 可调用模块和基本门 函数和任务 Function,task 只能描述组合逻辑 过程语句 Always语句,f语句,case、casex、casez语句 不支持initiali语句 过程块 Begin.end,命名block,disable 数据流 assign 综合时忽约延时信息 循环 For,while,forever 慎用,不同综合工具可能有差异

第五讲 数字系统设计的实现与验证 西安邮电学院通信工程系 Verilog HDL的综合要求 目前成熟的逻辑综合工具都支持RTL级设计的综合,行为级综合 只能在特定条件下进行,处于研究中。逻辑综合工具并不能处理随意 编写的verilog描述,下表列出综合工具通常能接受的verilog描述: 结构类型 关键字或描述 说明 端口 Input, output, inout 参数 parameter 模块定义 module 支持除===和!==外的操作符 信号和变量 Wire, reg, tri, integer 允许使用向量和数组表示 调用 模块,基本门 可调用模块和基本门 函数和任务 Function, task 只能描述组合逻辑 过程语句 Always语句, if 语句,case、casex、casez 语句 不支持initial语句 过程块 Begin. end, 命名block,disable 数据流 assign 综合时忽约延时信息 循环 For, while, forever 慎用,不同综合工具可能有差异

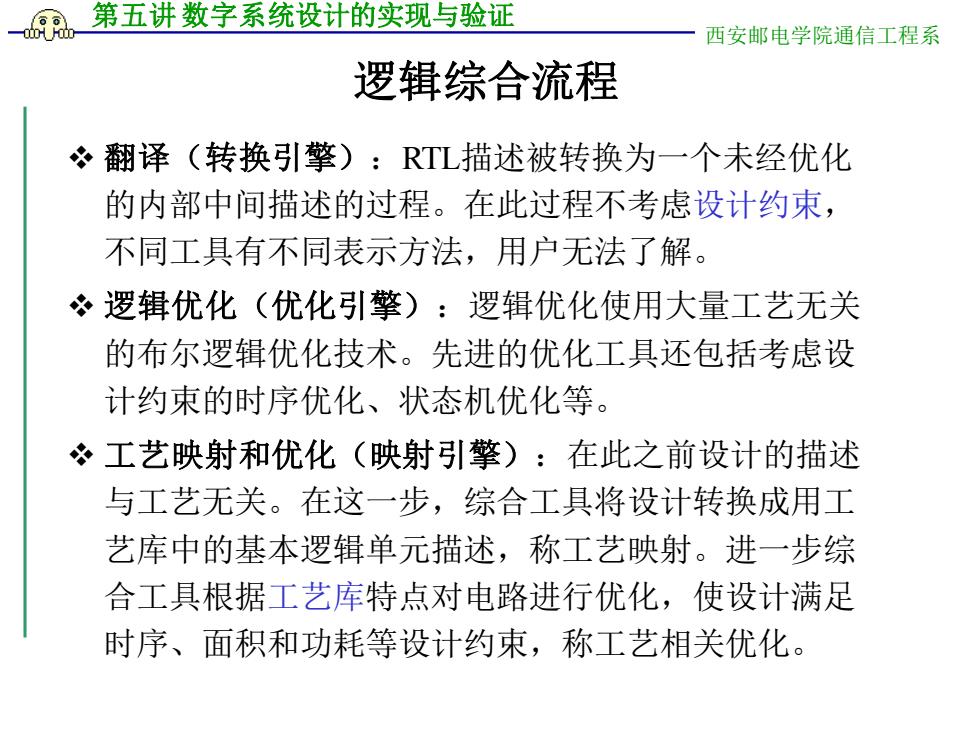

第五讲数字系统设计的实现与验证 -0001 西安邮电学院通信工程系 逻辑综合流程 。翻译(转换引擎):RTL描述被转换为一个未经优化 的内部中间描述的过程。在此过程不考虑设计约束, 不同工具有不同表示方法,用户无法了解。 冬逻辑优化(优化引擎):逻辑优化使用大量工艺无关 的布尔逻辑优化技术。先进的优化工具还包括考虑设 计约束的时序优化、状态机优化等。 冬工艺映射和优化(映射引擎):在此之前设计的描述 与工艺无关。在这一步,综合工具将设计转换成用工 艺库中的基本逻辑单元描述,称工艺映射。进一步综 合工具根据工艺库特点对电路进行优化,使设计满足 时序、面积和功耗等设计约束,称工艺相关优化

第五讲 数字系统设计的实现与验证 西安邮电学院通信工程系 逻辑综合流程 ❖ 翻译(转换引擎):RTL描述被转换为一个未经优化 的内部中间描述的过程。在此过程不考虑设计约束, 不同工具有不同表示方法,用户无法了解。 ❖ 逻辑优化(优化引擎):逻辑优化使用大量工艺无关 的布尔逻辑优化技术。先进的优化工具还包括考虑设 计约束的时序优化、状态机优化等。 ❖ 工艺映射和优化(映射引擎):在此之前设计的描述 与工艺无关。在这一步,综合工具将设计转换成用工 艺库中的基本逻辑单元描述,称工艺映射。进一步综 合工具根据工艺库特点对电路进行优化,使设计满足 时序、面积和功耗等设计约束,称工艺相关优化

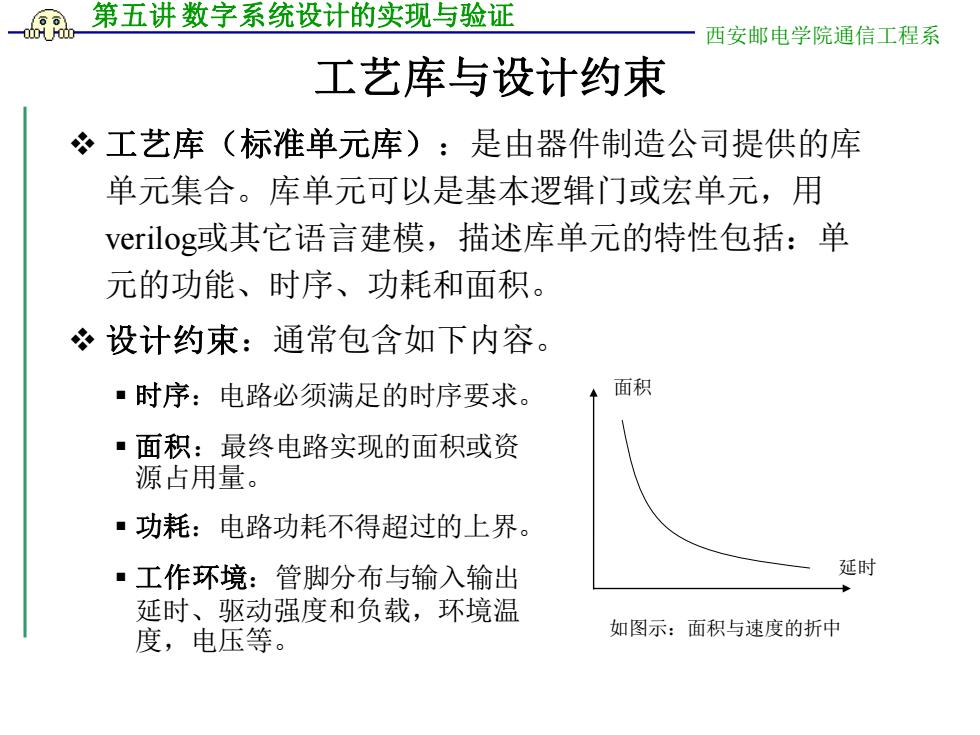

第五讲数字系统设计的实现与验证 -000 西安邮电学院通信工程系 工艺库与设计约束 工艺库(标准单元库):是由器件制造公司提供的库 单元集合。库单元可以是基本逻辑门或宏单元,用 verilog或其它语言建模,描述库单元的特性包括:单 元的功能、时序、功耗和面积。 冬设计约束:通常包含如下内容。 ■时序:电路必须满足的时序要求。 面积 面积:最终电路实现的面积或资 源占用量。 ·功耗:电路功耗不得超过的上界。 ·工作环境:管脚分布与输入输出 延时 延时、驱动强度和负载,环境温 度,电压等。 如图示:面积与速度的折中

第五讲 数字系统设计的实现与验证 西安邮电学院通信工程系 工艺库与设计约束 ❖ 工艺库(标准单元库):是由器件制造公司提供的库 单元集合。库单元可以是基本逻辑门或宏单元,用 verilog或其它语言建模,描述库单元的特性包括:单 元的功能、时序、功耗和面积。 ❖ 设计约束:通常包含如下内容。 ▪ 时序:电路必须满足的时序要求。 ▪ 面积:最终电路实现的面积或资 源占用量。 ▪ 功耗:电路功耗不得超过的上界。 ▪ 工作环境:管脚分布与输入输出 延时、驱动强度和负载,环境温 度,电压等。 延时 面积 如图示:面积与速度的折中

第五讲数字系统设计的实现与验证 西安邮电学院通信工程系 基于quartus2的逻辑综合与实现 常用的FPGA设计综合工具有Synplify、LeonardoSpectrum、FPGA Compiler等。Quartus.2软件自身也集成有综合工具,虽不如上述工具功 能强大,但也有自身的优点。 在使用综合工具时,一般不能直接修改综合的网表,只能通过修改 HDL设计或设计约束间接控制综合的结果。本讲以4bt串行乘法器设计 为例,介绍quartus.2的综合工具与实现设置,包括如下内容: 分配芯片管脚、时序约束输入。 综合工具设置。 冬综合网表的优化。 冬时序驱动的分配设置

第五讲 数字系统设计的实现与验证 西安邮电学院通信工程系 基于quartus2的逻辑综合与实现 常用的FPGA设计综合工具有Synplify、LeonardoSpectrum、FPGA Compiler等。Quartus2软件自身也集成有综合工具,虽不如上述工具功 能强大,但也有自身的优点。 在使用综合工具时,一般不能直接修改综合的网表,只能通过修改 HDL设计或设计约束间接控制综合的结果。本讲以4bit串行乘法器设计 为例,介绍quartus2的综合工具与实现设置,包括如下内容: ❖分配芯片管脚、时序约束输入。 ❖综合工具设置。 ❖综合网表的优化。 ❖时序驱动的分配设置

第五讲数字系统设计的实现与验证 西安邮电学院通信工程系 分配芯片管脚 Quartus II-D:/FPGA讲义/ULI/U皿T-夏ULT File Edit yiew Project Assignments Processing Ioo1s置indow Help Y卫evice. 可效’g必必 Status Lins Module Prog. Timing Settings. 2EDA Tool Settings. Settings. Ctrl+Shift+E Timing置izard., g Assignment Editor Ctrl+Shift+A 毯Tinr1 anner Ctrl+Shi ft+N 且emove Assignments.,. AN店R 吕Be地te Assigmments Project Navigatorx Back-Annotate Assignments. Entity △Cyclone:EP1C3T Import Assignments. ART 由-意y-nlt4 Export Assignments.,· Assignment (Time)Groups. Timing Closure Eloorplan 打开管脚 LogicLock Regions Window Alt+L 编辑器 Design Partitions Window Alt+D

第五讲 数字系统设计的实现与验证 西安邮电学院通信工程系 分配芯片管脚 打开管脚 编辑器