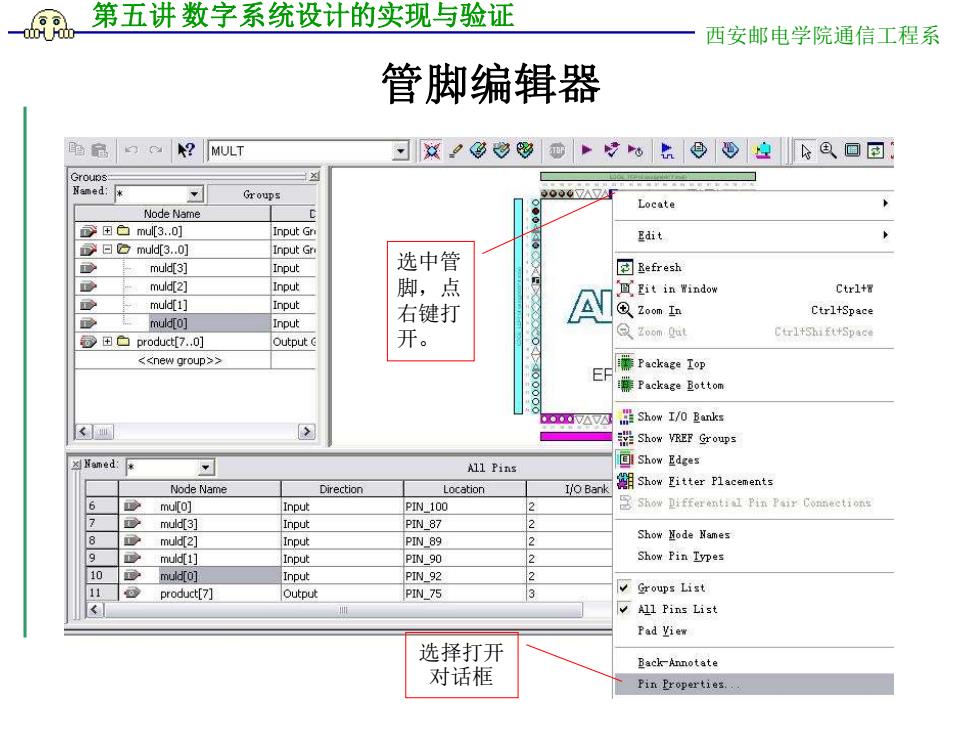

6 第五讲数字系统设计的实现与验证 西安邮电学院通信工程系 管脚编辑器 ? MULT 可深9必必罗画境⑨四迎 Grouns a通ed; Groups Locate Node Name 田白mu[3.0] Input Gn Edit 曰muld[3.oj Input Gn D muld[3] Input 选中管 图Refresh D muld[2] Input 脚,点 可it in indow Ctr1+冒 。 muld[1] Input 右键打 ®Zoom In Ctrl+Space muld[o] Input 田白product[7.o] Output 开。 Zoom Qut Ctrl+Shift+Space <<new group>> Package Iop ER Package Bottom o●av△v 器Show I/0 Eanks 器Show VR2 F Groups x Named:* 习 All Pins 回Show Edges Node Name Direction Location I/o Bank Show Eitter Placements 6 mul[o] Input PIN_100 Show pifferential Pin Pair Connections muld[3] Input PIN_87 2 8 muld[2] Input PIN_89 2 Show Node Names 9 > muld[1] Input PIN 90 3 Show Pin Types 10 0 muld[0] Input PIN_92 2 11 product[7] Output PIN_75 3 Groups List All Pins List Pad View 选择打开 Back-Annotate 对话框 Pin Properties

第五讲 数字系统设计的实现与验证 西安邮电学院通信工程系 管脚编辑器 选中管 脚,点 右键打 开。 选择打开 对话框

第五讲数字系统设计的实现与验证 西安邮电学院通信工程系 管脚编辑器 白 O ? MULT 可x’g必必@6恩四煌 众®回 Grouns Named:* Groups Node Name 田□mu[3.0则 Input Gr Top View 日omud[3nl Inout Gr > Pin Properties > > Pin number: PIN 92 AUERA D Node name: muld[0] ○田向pr( 1/0 standard: LVTTL (default) Cyclone Reserved: EP1C3T100C8 Properties: Name Value 1/0 Bank 2 General Function Column 1/0 x Named: Special Function DPCLK2/DQS1T Pad ID 110 Pins Filter Pins:al VREF Pad ID 109 I/o Bank VREF Group I/O Standar 6 2 B2_N2 LVTTL (default) 7 OK Cancel 2 打开下 B2_N1 LVTTL (default) 8 B2_N1 LVTTL (default) 9 0 muo Inpuc PIN 90 2 拉菜单, B2_N2 LVTTL (default) 10 心 muld[o] Input PIN_92 2 选择分 B2_N2 LVTTL (default) 11 product[7] Output PIN_75 3 配的信 B3 NO LVTTL (default) 号

第五讲 数字系统设计的实现与验证 西安邮电学院通信工程系 管脚编辑器 打开下 拉菜单, 选择分 配的信 号

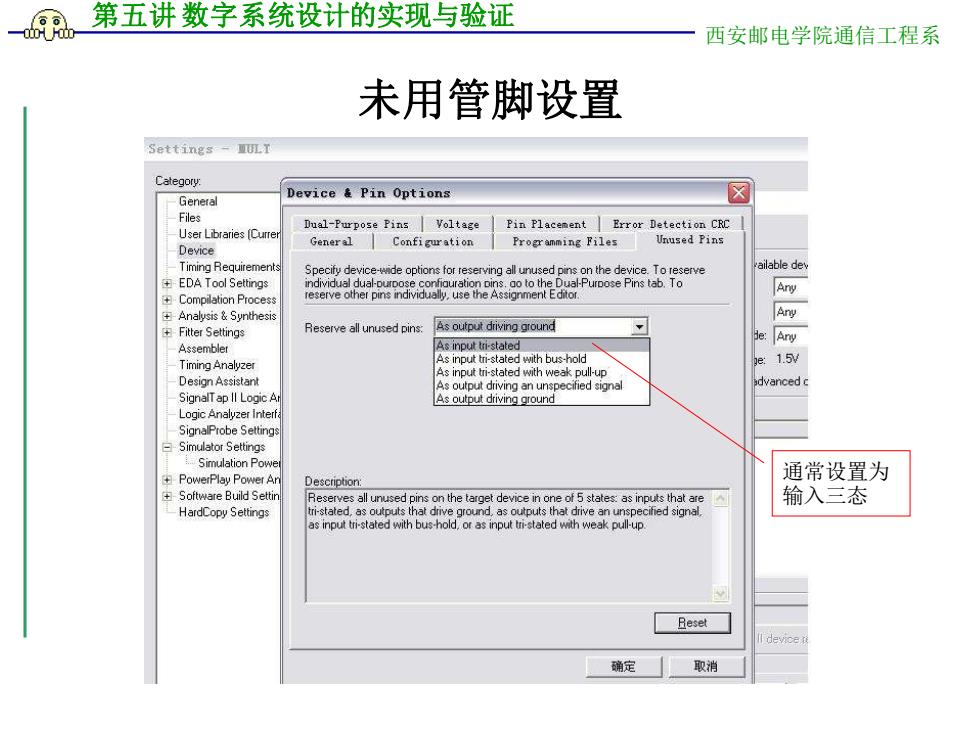

6 第五讲数字系统设计的实现与验证 西安邮电学院通信工程系 未用管脚设置 Settings MULT Category. General Device Pin Options ☒ Files Dual-Purpose Pins Voltage Pin Placement Error Detection CRC User Libraries (Currer Device General Configuration Programming Files Unused Pins Timing Requirements Specify device-wide options for reserving all unused pins on the device.To reserve ailable dev 由EDA Tool Settings individual dual-ouDose confiouration Dins.ao to the Dual-Purpose Pins tab.To reserve other pins individually,use the Assignment Editor. Any 由-Compilation Process 年-Analysis&Synthesis Any 年Fitter Settings Reserve all unused pins: As output driving ground de:Any Assembler As input tri-stated Timing Analyzer As input tri-stated with bus-hold 1.5/ As input tri-stated with weak pull-up Design Assistant As output driving an unspecified signal dvanced c SignalTap ll Logic Ar As output driving ground Logic Analyzer Interf SignalProbe Settings Simulator Settings Simulation Power 由-PowerPlay Power An 通常设置为 Description: Software Build Settin Reserves all unused pins on the target device in one of 5 states:as inputs that are 输入三态 HardCopy Settings tri-stated,as outputs that drive ground,as outputs that drive an unspecified signal. as input tri-stated with bus-hold,or as input tri-stated with weak pull-up. Reset ll device我 确定 取消

第五讲 数字系统设计的实现与验证 西安邮电学院通信工程系 未用管脚设置 通常设置为 输入三态

第五讲数字系统设计的实现与验证 西安邮电学院通信工程系 全局时序约束输入 将芯片看成一组D触发器,输入输出管脚有: Assigments Processing Tools Find y卫eice Tsu、Th:管脚输入的建立时间和保持时间。 Rins Tco:管脚上时钟到寄存器输出管脚的延时。 Timing Settings. Tpd:管脚到管脚的最大延时。 EDA Settings MULT Category: General Files User Libraries (Current Project] Specify himing requirements and options.Individual timing assignments can be made through the Device Assignment Editor. Timing Requirements&Options EDA Tool Settings Delay requirements Complation Process Settings tsu: ns Report minimum timing checks Early Timing Estimate Minimum delay requirements- Incremental Compilation tco: ns Analysis Synthesis Settings Minimum.tco. 白Fitter Settings tpd: ns Mi7以rmpd Physical Synthesis Optimizations h ns Assembler Timing Analyzer Design Assistant Clock Settings SignalT ap ll Logic Analyzer Default required fmax: Logic Analyzer Interface SignaProbe Settings Individual Clocks. 全局默认时 白-Simulator Settings Simulation Power More Settings. 钟频率设置 PowerPlay Power Analyzer Settings 独立时 Software Build Settings HardCopy Settings 钟设置 Description

第五讲 数字系统设计的实现与验证 西安邮电学院通信工程系 全局时序约束输入 将芯片看成一组D触发器,输入输出管脚有: Tsu、Th:管脚输入的建立时间和保持时间。 Tco:管脚上时钟到寄存器输出管脚的延时。 Tpd:管脚到管脚的最大延时。 全局默认时 钟频率设置 独立时 钟设置