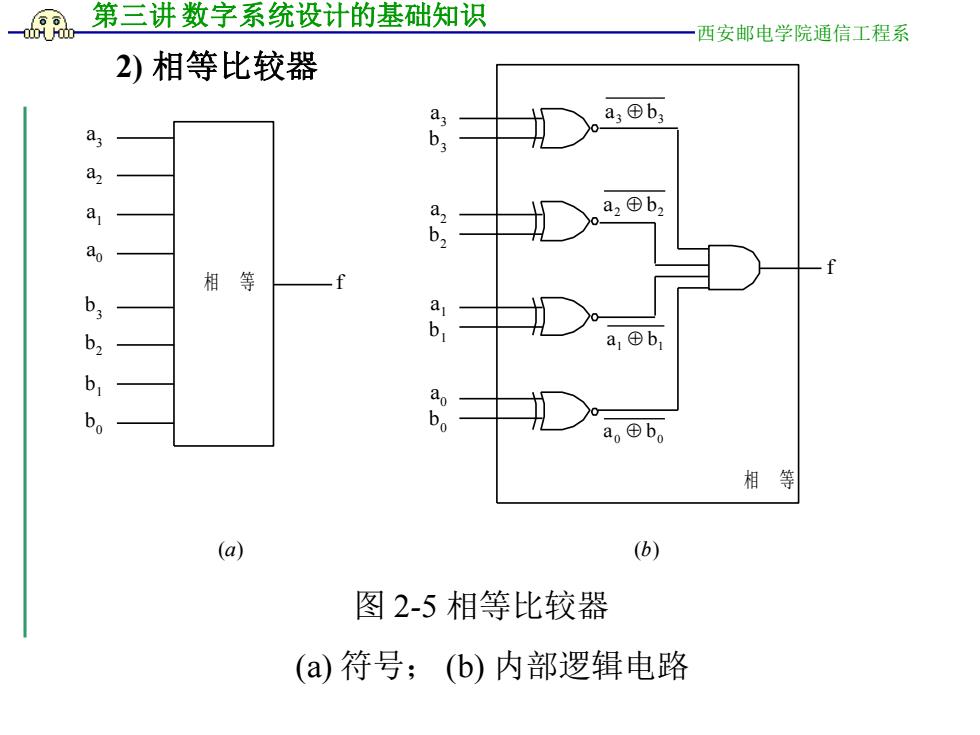

第三讲数字系统设计的基础知识 西安邮电学院通信工程系 2)相等比较器 523 a,⊕b3 a2⊕b2 相等 -f No a1⊕b1 ao⊕bo 相 等 (a) (b) 图2-5相等比较器 (a)符号;(b)内部逻辑电路

第三讲 数字系统设计的基础知识 西安邮电学院通信工程系 图 2-5 相等比较器 (a) 符号; (b) 内部逻辑电路 相 等 a3 a2 a1 a0 b 3 b2 b1 b0 f a3 b3 a 2 b2 a1 b1 a0 b0 f 3 3 a b 2 b2 a 1 1 a b 0 0 a b 相 等 (a) (b) 2) 相等比较器

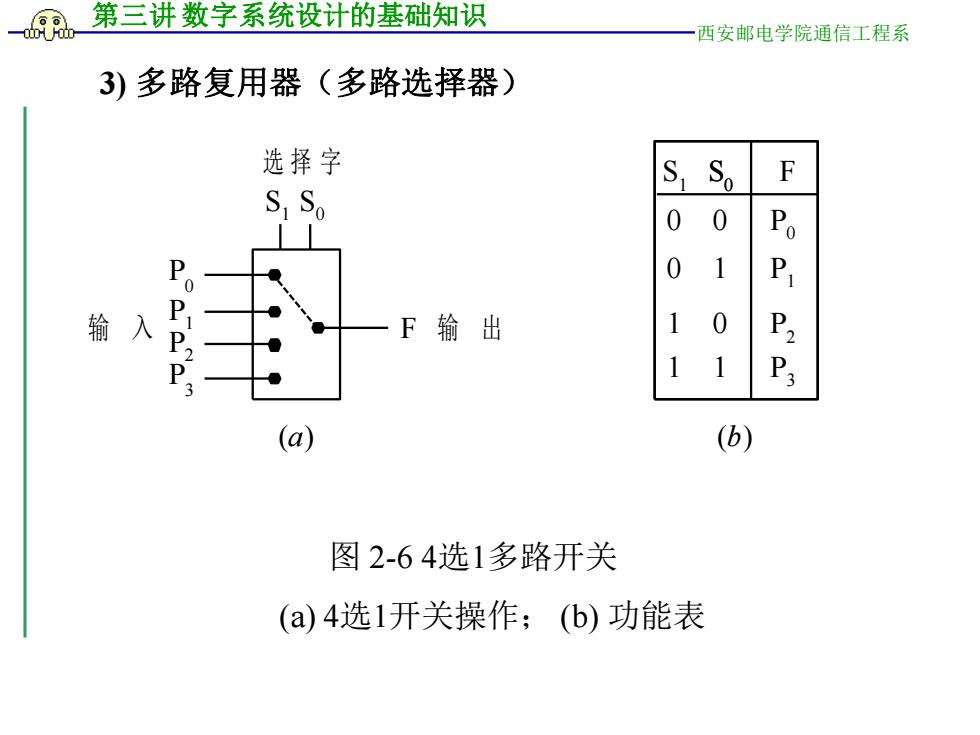

第三讲数字系统设计的基础知识 西安邮电学院通信工程系 3)多路复用器(多路选择器) 选择字 S So F S:So 0 0 Po 0 P 输 入 F输出 10 11 P (a) (b) 图2-64选1多路开关 (a)4选1开关操作;(b)功能表

第三讲 数字系统设计的基础知识 西安邮电学院通信工程系 图 2-6 4选1多路开关 (a) 4选1开关操作; (b) 功能表 P0 P1 P2 P3 S1 S0 输 入 F 输 出 选 择 字 S1 S0 0 0 0 1 1 0 1 1 F P0 P1 P2 P3 S0 (a) (b) 3) 多路复用器(多路选择器)

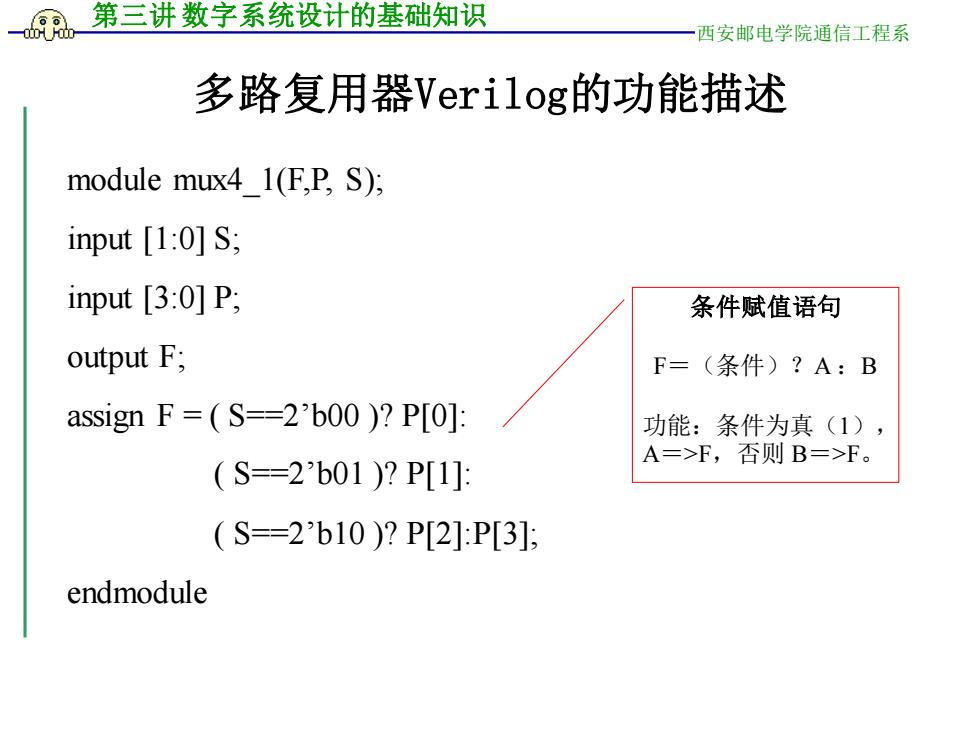

第三讲数字系统设计的基础知识 西安邮电学院通信工程系 多路复用器Verilogl的功能描述 module mux4 1(F,P,S); input [1:0]S; input [3:0]P; 条件赋值语句 output F; F=(条件)?A:B assign F=(S==2'b00)?P[O]: 功能:条件为真(1), A=>F,否则B=>F。 (S=2b01)?P[1]: (S==2b10)?P[2]P[3]; endmodule

第三讲 数字系统设计的基础知识 西安邮电学院通信工程系 多路复用器Verilog的功能描述 module mux4_1(F,P, S); input [1:0] S; input [3:0] P; output F; assign F = ( S==2’b00 )? P[0]: ( S==2’b01 )? P[1]: ( S==2’b10 )? P[2]:P[3]; endmodule 条件赋值语句 F=(条件)?A :B 功能:条件为真(1), A=>F,否则 B=>F

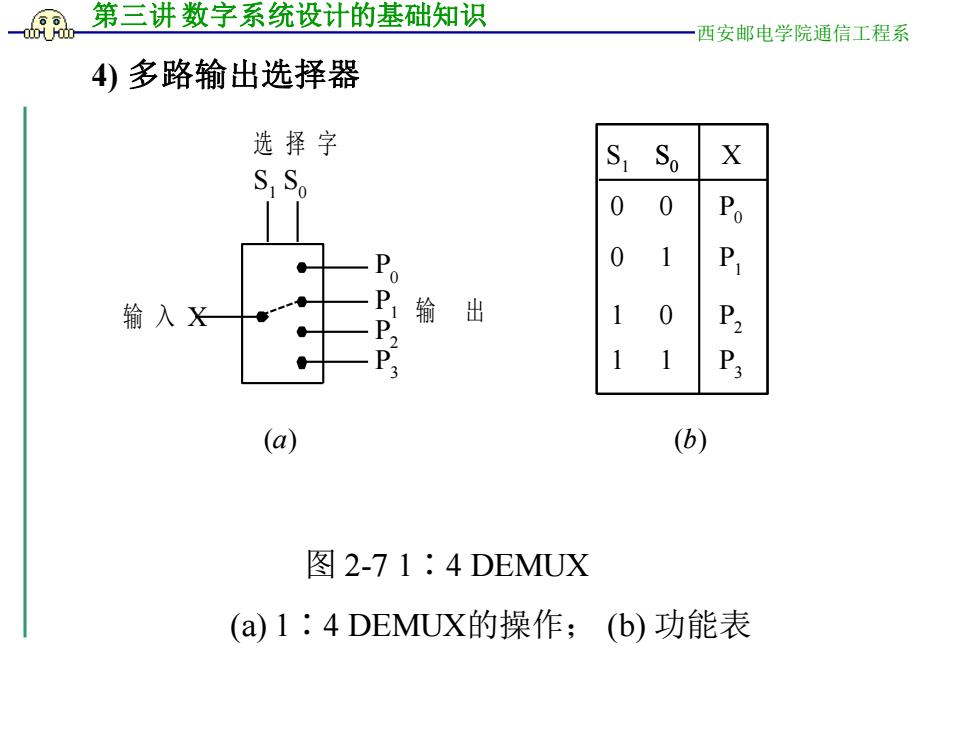

第三讲数字系统设计的基础知识 西安邮电学院通信工程系 4)多路输出选择器 选择字 S X SSo 0 0 Po 0 P 输入X 输 出 10 1 P (a) (b) 图2-71:4 DEMUX (a)1:4 DEMUX的操作;(b)功能表

第三讲 数字系统设计的基础知识 西安邮电学院通信工程系 图 2-7 1∶4 DEMUX (a) 1∶4 DEMUX的操作; (b) 功能表 输 入 X 输 出 (a) (b) P0 P1 P2 P3 S0 S1 选择字 S1 S0 0 0 0 1 1 0 1 1 X P0 P1 P2 P3 S0 4) 多路输出选择器

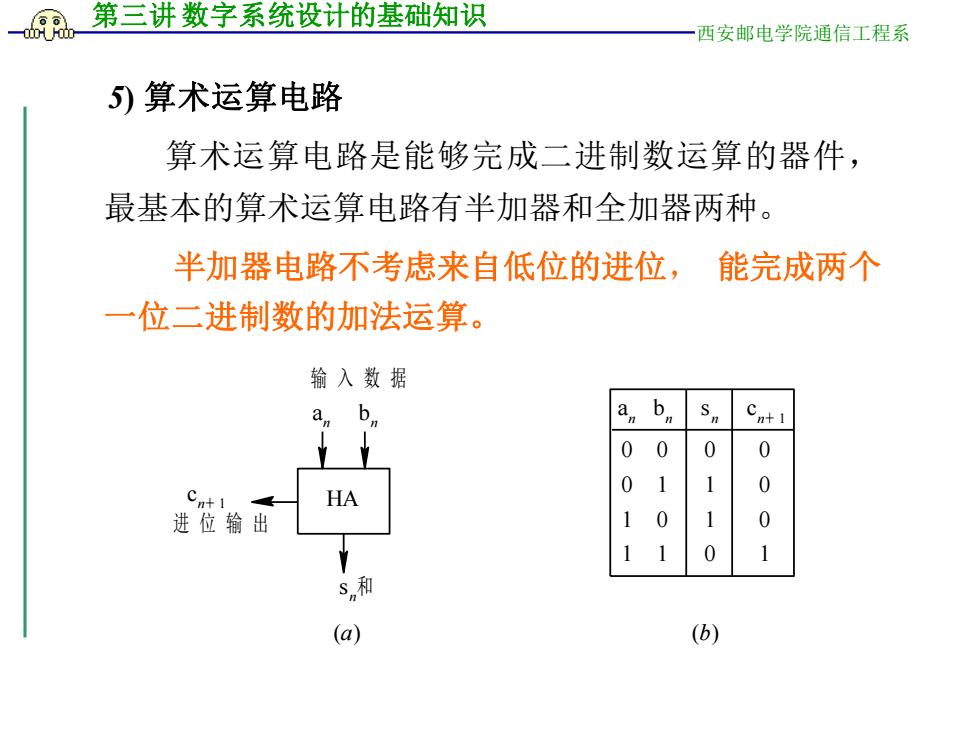

第三讲数字系统设计的基础知识 西安邮电学院通信工程系 5)算术运算电路 算术运算电路是能够完成二进制数运算的器件, 最基本的算术运算电路有半加器和全加器两种。 半加器电路不考虑来自低位的进位,能完成两个 一位二进制数的加法运算。 输入数据 a Sn Cn+1 0 0 0 0 0 1 1 0 Cn+1 HA 进位输出 1 0 1 0 1 0 1 S,和 (a) (b)

第三讲 数字系统设计的基础知识 西安邮电学院通信工程系 5) 算术运算电路 算术运算电路是能够完成二进制数运算的器件, 最基本的算术运算电路有半加器和全加器两种。 半加器电路不考虑来自低位的进位, 能完成两个 一位二进制数的加法运算。 HA 输入数据 an bn s n 和 cn+ 1 进位输出 0 0 0 1 1 0 1 1 0 1 1 0 (a) (b) a n b n s n c n+ 1 0 0 0 1