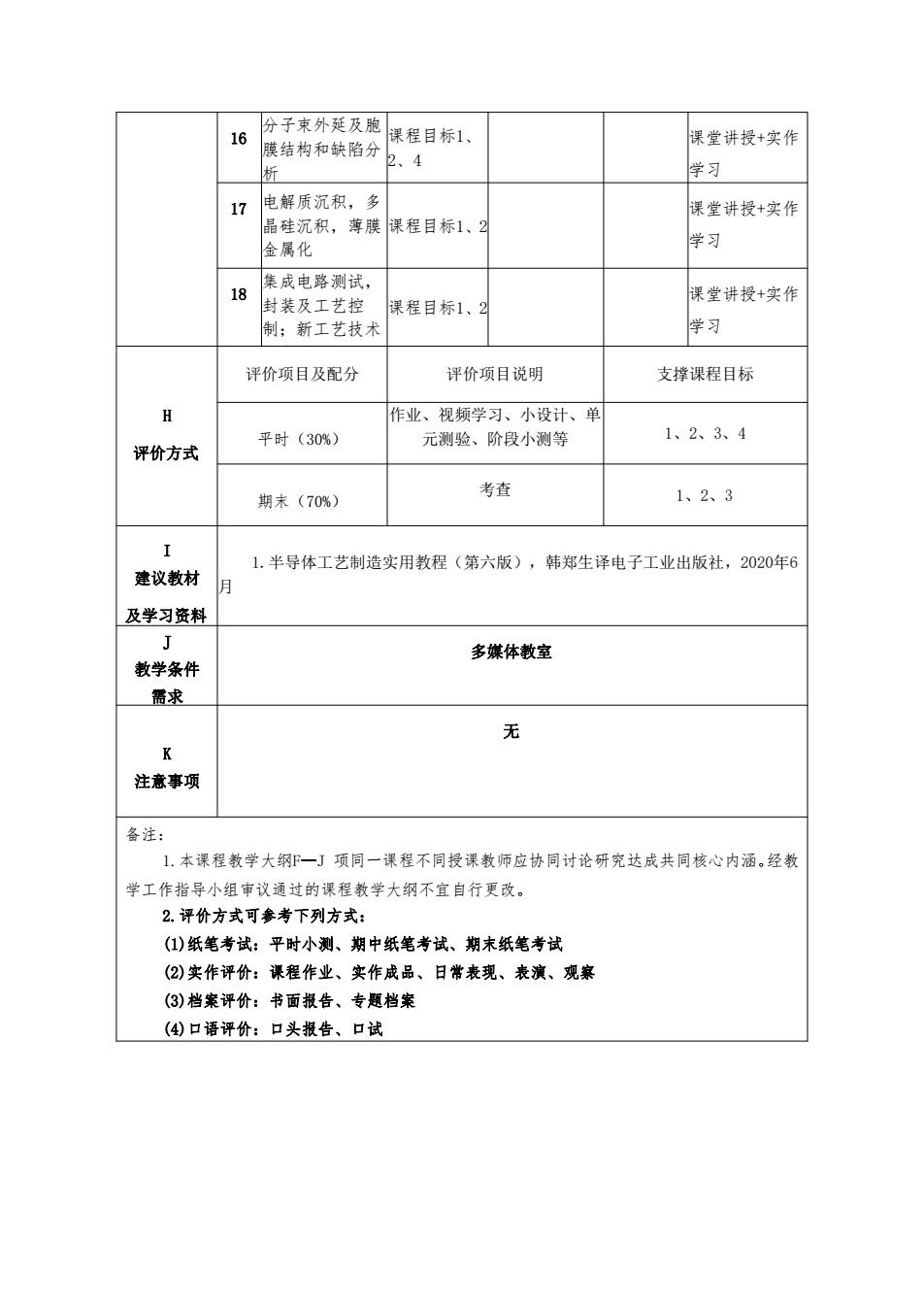

份子束外延及脆课程目标1、 膜结构和缺陷分 课堂讲授+实作 .4 学习 17 电解质沉积,多 课堂讲授+实作 品硅沉积薄膜课程目标1、》 金属化 学习 线成电路测试」 18 封装及工艺控 果程目标1、2 课堂讲授+实作 制:新工艺技 学习 评价项目及配分 评价项目说明 支撑课程目标 作业、视频学习、小设计、单 平时(30%) 1、2、3、4 评价方式 元测验、阶段小测等 期末(70%) 考查 1、2、3 1.半导体工艺制造实用教程(第六版),韩郑生译电子工业出版社,2020年6 建议教材 月 及学习资料 多媒体救室 教学条件 需求 无 注意事项 备注: 1,本课程教学大纲F一」项同一课程不同授课教师应协同讨论研究达成共同核心内涵,经教 学工作指导小组审议通过的课程教学大纲不宜自行更改。 2.评价方式可参考下列方式: (1)纸笔考试:平时小测、期中纸笔考试、期末纸笔考试 (2②)实作评价:课程作业、实作成品、日常表现、表演、观寒 (3)档案评价:书面报告、专题档案 (④口语评价:口头报告、口试

16 分子束外延及胞 膜结构和缺陷分 析 课程目标1、 2、4 课堂讲授+实作 学习 17 电解质沉积,多 晶硅沉积,薄膜 金属化 课程目标1、2 课堂讲授+实作 学习 18 集成电路测试, 封装及工艺控 制;新工艺技术 未来展望 课程目标1、2 课堂讲授+实作 学习 H 评价方式 评价项目及配分 评价项目说明 支撑课程目标 平时(30%) 作业、视频学习、小设计、单 元测验、阶段小测等 1、2、3、4 期末(70%) 考查 1、2、3 I 建议教材 及学习资料 1.半导体工艺制造实用教程(第六版),韩郑生译电子工业出版社,2020年6 月 J 教学条件 需求 多媒体教室 K 注意事项 无 备注: 1.本课程教学大纲F—J 项同一课程不同授课教师应协同讨论研究达成共同核心内涵。经教 学工作指导小组审议通过的课程教学大纲不宜自行更改。 2.评价方式可参考下列方式: (1)纸笔考试:平时小测、期中纸笔考试、期末纸笔考试 (2)实作评价:课程作业、实作成品、日常表现、表演、观察 (3)档案评价:书面报告、专题档案 (4)口语评价:口头报告、口试

课程教学大纲起草团队成员签名: 专家组审定意见: 申批意见 专家组成员签名: 学院教学工作指导小组审议意见: 教学工作指导小组组长: 年月日

审批意见 课程教学大纲起草团队成员签名: 专家组审定意见: 专家组成员签名: 学院教学工作指导小组审议意见: 教学工作指导小组组长: 年 月 日

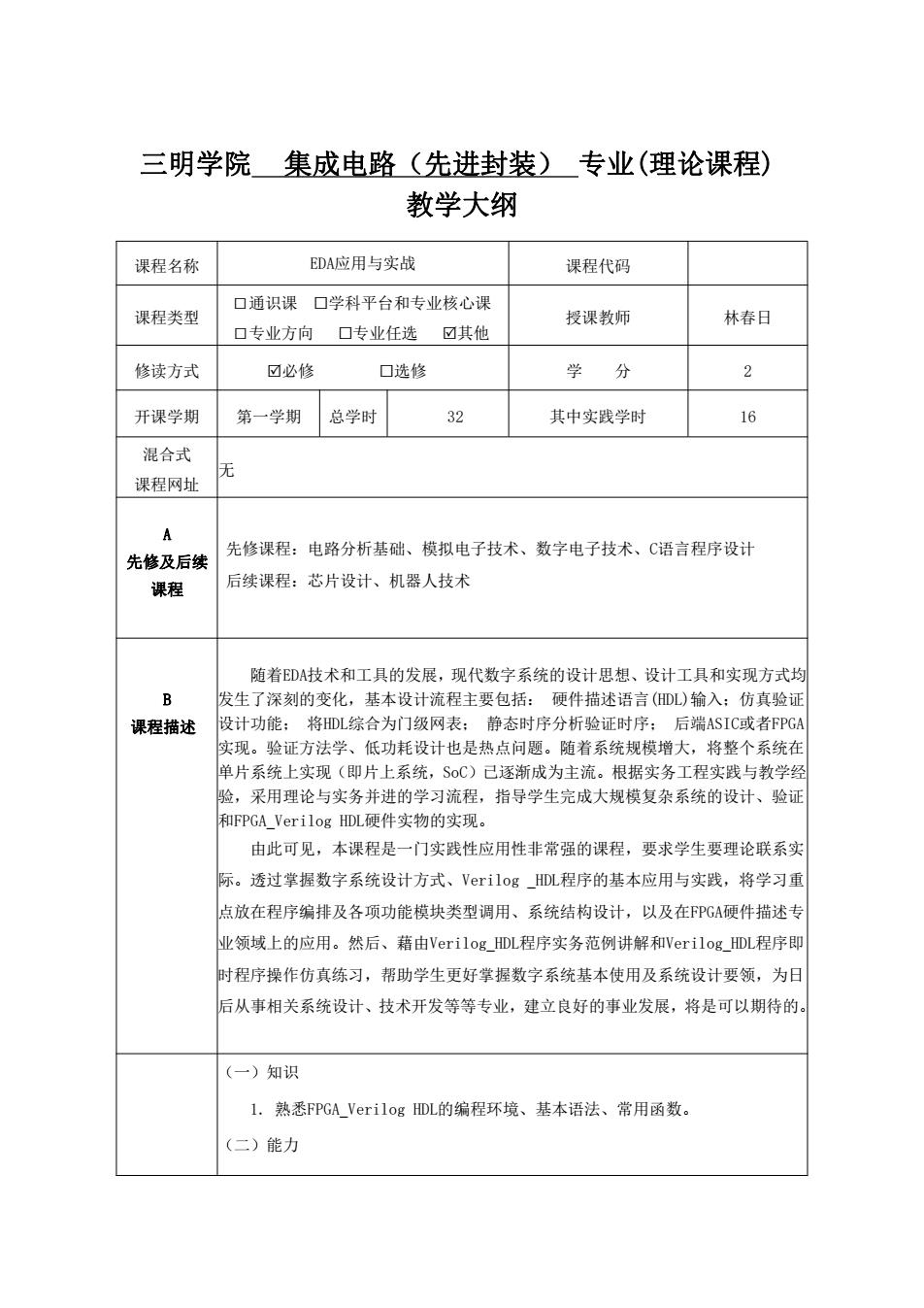

三明学院集成电路(先进封装)专业(理论课程) 教学大纲 课程名称 EDA应用与实战 课程代码 口通识课口学科平台和专业核心课 课程类型 授课教师 林春日 口专业方向口专业任选☑其他 修读方式 ☑必修 口选修 学分 开课学期 第一学期总学时 32 其中实践学时 16 混合式 课程网址 无 A 先修及后续 先修课程:电路分析基础、模拟电子技术、数字电子技术、C语言程序设计 课程 后续课程:芯片设计、机器人技术 随若DA技术和工具的发展,现代数字系统的设计思想、设计工具和实现方式 B 发生了深刻的变化,基本设计流程主要包括:硬件描述语言(D)输入:仿真验证 课程描述设计功能:将DL综合为门级网表:静态时序分析验证时序:后端ASIC或者FPGd 实现。验证方法学、低功耗设计也是热点间题。随若系统规模增大,将整个系统在 单片系统上实现(即片上系统,SC)己逐渐成为主流。根据实务工程实践与教学 险,采用理论与实务并进的学习流程,指导学生完成大规模复杂系统的设计、验 和FPGA Verilog HDL硬件实物的实现。 由此可见,本课程是一门实践性应用性非常强的课程,要求学生要理论联系实 际。透过掌握数字系统设计方式、Verilog_HDL程序的基本应用与实践,将学习重 点放在程序编排及各项功能模块类型调用、系统结构设计,以及在FPG弘硬件描述专 业领域上的应用。然后、藉由Verilog_HDL程序实务范例讲解和Verilog_.HDL程序即 时程序操作仿真练习,帮助学生更好掌握数字系统基本使用及系统设计要领,为日 后从事相关系统设计、技术开发等等专业,建立良好的事业发展,将是可以期待的 (一)知识 l.熟悉FPGA_Verilog HDLf的编程环境、基本语法、常用函数。 (二)能力

三明学院 集成电路(先进封装) 专业(理论课程) 教学大纲 课程名称 EDA应用与实战 课程代码 课程类型 通识课 学科平台和专业核心课 专业方向 专业任选 其他 授课教师 林春日 修读方式 必修 选修 学 分 2 开课学期 第一学期 总学时 32 其中实践学时 16 混合式 课程网址 无 A 先修及后续 课程 先修课程:电路分析基础、模拟电子技术、数字电子技术、C语言程序设计 后续课程:芯片设计、机器人技术 B 课程描述 随着EDA技术和工具的发展,现代数字系统的设计思想、设计工具和实现方式均 发生了深刻的变化,基本设计流程主要包括: 硬件描述语言(HDL)输入;仿真验证 设计功能; 将HDL综合为门级网表; 静态时序分析验证时序; 后端ASIC或者FPGA 实现。验证方法学、低功耗设计也是热点问题。随着系统规模增大,将整个系统在 单片系统上实现(即片上系统,SoC)已逐渐成为主流。根据实务工程实践与教学经 验,采用理论与实务并进的学习流程,指导学生完成大规模复杂系统的设计、验证 和FPGA_Verilog HDL硬件实物的实现。 由此可见,本课程是一门实践性应用性非常强的课程,要求学生要理论联系实 际。透过掌握数字系统设计方式、Verilog _HDL程序的基本应用与实践,将学习重 点放在程序编排及各项功能模块类型调用、系统结构设计,以及在FPGA硬件描述专 业领域上的应用。然后、藉由Verilog_HDL程序实务范例讲解和Verilog_HDL程序即 时程序操作仿真练习,帮助学生更好掌握数字系统基本使用及系统设计要领,为日 后从事相关系统设计、技术开发等等专业,建立良好的事业发展,将是可以期待的。 (一)知识 1. 熟悉FPGA_Verilog HDL的编程环境、基本语法、常用函数。 (二)能力