中国科学技术大学物理系微电子考业 •栅氧化层厚度缩小的物理限制 随器件特征尺寸的缩小,沟道长度、栅氧化层厚度、源漏与 沟道结深尺度需要按比例缩小(L∝TxX)。当栅氧化层厚 度缩小到2nm以下时,量子直接隧穿效应将变得非常显著。 E+03 E+02 SiO2 Gate Leakage Gate E+01 (from literature) Gate Oxide E+00 .E-01 .E-02 Source Drain .E-03 .E-04 Gate .E-05 .E-06 5 10 15 20 25 Physical Tox (A) Principle of Semiconductor Devices 2022/12/25 6

中国科学技术大学物理系微电子专业 2022/12/25 Sunday 6 Principle of Semiconductor Devices

中国科学技术大学物理系微电子考业 ·高K栅介质和金属栅电极的需求 利用高K栅介质替代SO,作为栅介质层材料,由于在维持相 同等效氧化层厚度的情形下,可使用厚的介质层厚度,从而 显著减小量子直接隧穿效应引起的栅泄漏电流。 等效氧化层厚度(Equivalent Gate Oxide Thickness,EOT)是指 厚度为t介电常数为6的介质 材料等效为SO,对应的厚度: Source Drain C= eH币 tox High K Gate Dielectric EOT= Hi Principle of Semiconductor Devices 2022/12/25 7

中国科学技术大学物理系微电子专业 2022/12/25 Sunday 7 Principle of Semiconductor Devices

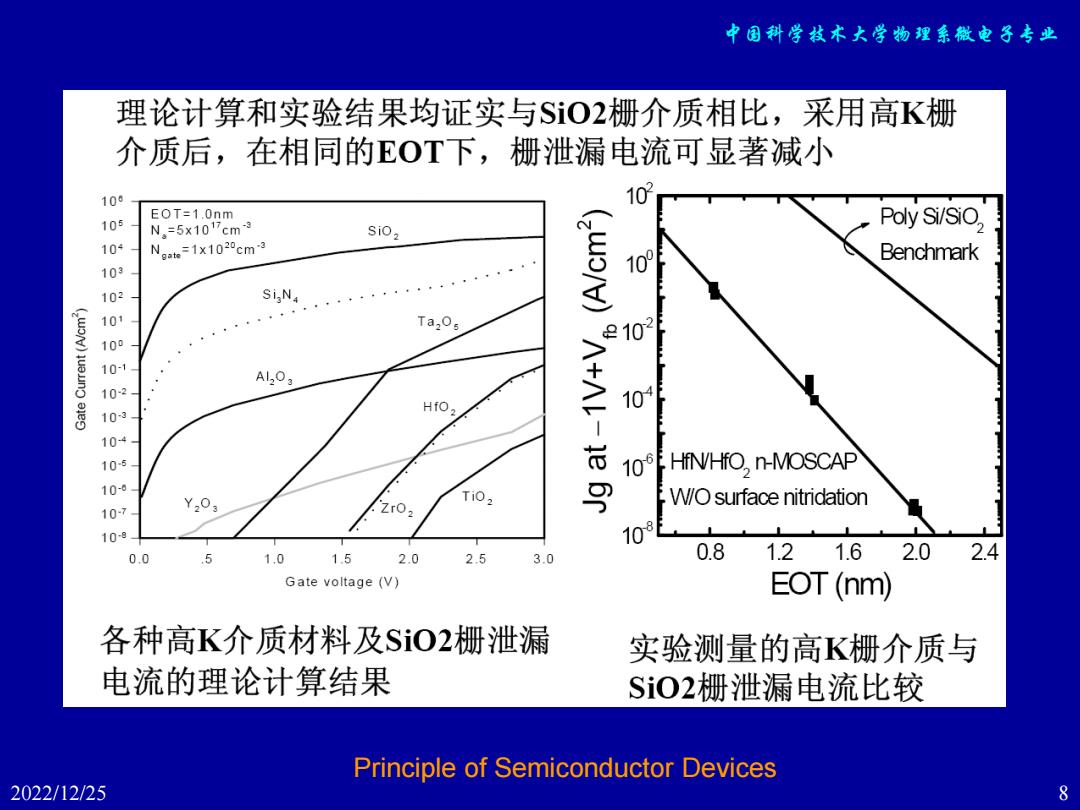

中国科学枝术大学物理系微电子专业 理论计算和实验结果均证实与SiO2栅介质相比,采用高K栅 介质后,在相同的EOT下, 栅泄漏电流可显著减小 100 10 105 EOT=1.0nm N,=5x1017cm3 SiO2 Poly Si/Sio, 104 Ngate=1x1020cm3 Benchmark 109 10 102 SigN4 10 Ta2Os 102 100 10-1 Al2O3 102 10-3 Hfo, 104 104 10-5 105 HfN/HfO,n-MOSCAP 10-6 10-7 Y2O3 'Zr02 习 W/O surface nitridation 10-8 108 0.0 1.0 1.5 2.0 2.5 3.0 0.8 1.2 1.6 2.0 2.4 Gate voltage (V) EOT(nm) 各种高K介质材料及SO2栅泄漏 实验测量的高K栅介质与 电流的理论计算结果 SO2栅泄漏电流比较 Principle of Semiconductor Devices 2022/12/25 8

中国科学技术大学物理系微电子专业 2022/12/25 Sunday 8 Principle of Semiconductor Devices

中国科学技术大学物理系微电子考业 由于Si/SiO2 Gate +ve voltage appled) 纯硅基 MOS器件具 的SiO薄膜能 e e 够阻止更多 e e 硅与衬底 硅的功函数 高器件开 关速度。 然而,当特 首效应,显 著增大器件 PSub 上要求进一步 提高栅极电 T丁小甲VUZ公于义天u, 随之而来的 是栅电极漏电流的增加。当SiO2作为栅电极绝缘层的厚度低于5nm 时,漏电流变得无法忍受。 解决上述问题的方法就是使用高介电常数绝缘材料取代SO2,采 用高k介质材料可以在不增加电学厚度的前提下允许增加绝缘层厚 度,从而能够降低漏电流。 Principle of Semiconductor Devices 2022/12/25 9

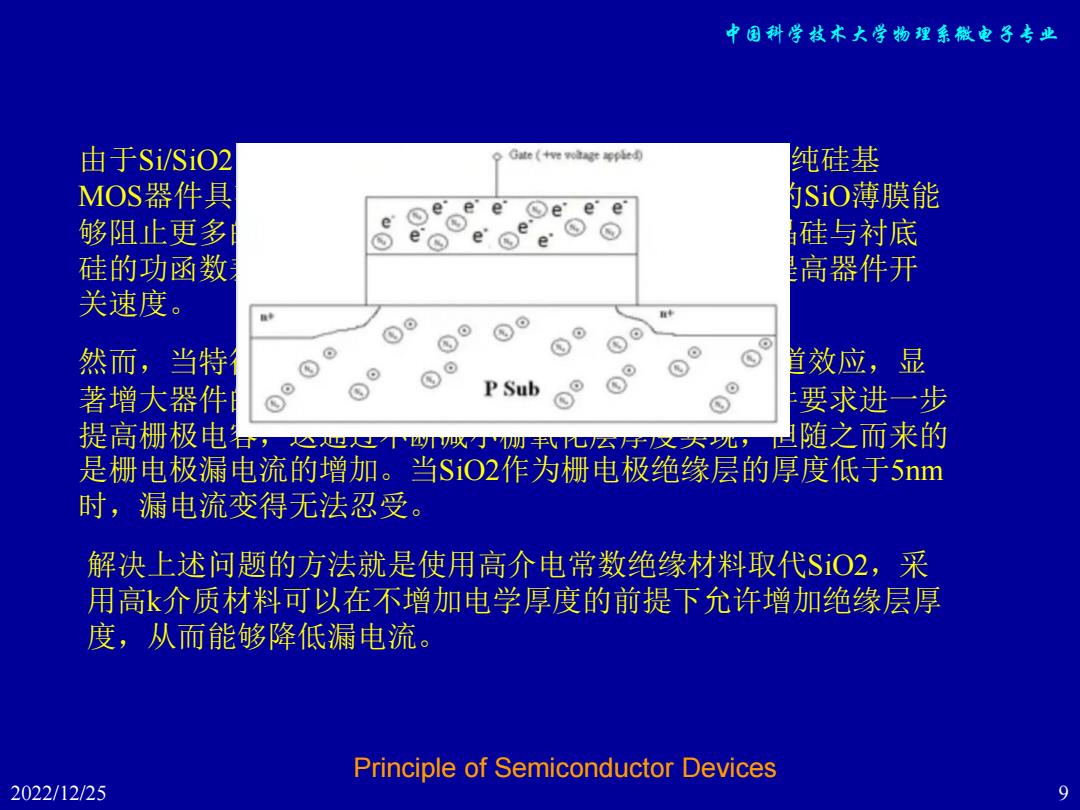

中国科学技术大学物理系微电子专业 2022/12/25 Sunday 9 Principle of Semiconductor Devices 由于Si/SiO2良好的界面特性以及SiO薄膜的优异性能,纯硅基 MOS器件具有优异的界面性能和热稳定性,并且致密的SiO薄膜能 够阻止更多的氧气和水分子进入栅介质层。另外,多晶硅与衬底 硅的功函数差值较小,有利于降低器件的阈值电压,提高器件开 关速度。 然而,当特征长度降低至65nm节点时,就会出现短沟道效应,显 著增大器件的功耗。为控制短沟道效应,更小尺寸器件要求进一步 提高栅极电容,这通过不断减小栅氧化层厚度实现,但随之而来的 是栅电极漏电流的增加。当SiO2作为栅电极绝缘层的厚度低于5nm 时,漏电流变得无法忍受。 解决上述问题的方法就是使用高介电常数绝缘材料取代SiO2,采 用高k介质材料可以在不增加电学厚度的前提下允许增加绝缘层厚 度,从而能够降低漏电流

中国科学技术大学物理系微电子专业 经过反复实验,基于铪Hf的ig-k绝缘材料取代SiO2作为栅电 极的绝缘层,在一定程度上缓解SO2厚度减小引起的隧穿效应, 进而减小泄漏电流,降低器件功耗。然而,当特征长度降至 45nm时,多晶硅/高k基MOS器件出现严重的多晶硅耗尽效应。 多晶硅的高电阻率也严重影响了MOS器件的高频特性。 在早期的高介电常数材料研究中就己经发现了高k介质与多晶 硅栅电极不匹配的问题。这一问题不仅会导致在高介电材料 与多晶硅材料的界面上产生大量的缺陷,还会降低器件的电 子迁移率。后一问题是由于电荷散射而引起的,这也是将这 两种材料结合在一起的固有表现。因此金属栅代替多晶硅栅, 被用于纳米晶体管和先进晶体管结构。 金属栅极是为了和高k栅介质材料兼容提出的,一方面金属作 为良好导体,不会产生耗尽层,有效消除了多晶硅耗尽效应, 同时也使金属栅极无需通过参杂提高导电性。另一方面,与 多晶硅相比,金属栅极材料自由电子浓度远大于反型层载流 子浓度,使得金属栅极能有效抑制高k介质低能光学声子与沟 道载流子耦合,从而降低声子散射,提高载流子迁移率。 Principle of Semiconductor Devices 2022/12/25 10

中国科学技术大学物理系微电子专业 2022/12/25 Sunday 10 Principle of Semiconductor Devices 经过反复实验,基于铪Hf的hig-k绝缘材料取代SiO2作为栅电 极的绝缘层,在一定程度上缓解SiO2厚度减小引起的隧穿效应, 进而减小泄漏电流,降低器件功耗。然而,当特征长度降至 45nm时,多晶硅/高k基MOS器件出现严重的多晶硅耗尽效应。 多晶硅的高电阻率也严重影响了MOS器件的高频特性。 在早期的高介电常数材料研究中就已经发现了高k介质与多晶 硅栅电极不匹配的问题。这一问题不仅会导致在高介电材料 与多晶硅材料的界面上产生大量的缺陷,还会降低器件的电 子迁移率。后一问题是由于电荷散射而引起的,这也是将这 两种材料结合在一起的固有表现。因此金属栅代替多晶硅栅, 被用于纳米晶体管和先进晶体管结构。 金属栅极是为了和高k栅介质材料兼容提出的,一方面金属作 为良好导体,不会产生耗尽层,有效消除了多晶硅耗尽效应, 同时也使金属栅极无需通过掺杂提高导电性。另一方面,与 多晶硅相比,金属栅极材料自由电子浓度远大于反型层载流 子浓度,使得金属栅极能有效抑制高k介质低能光学声子与沟 道载流子耦合,从而降低声子散射,提高载流子迁移率