第一讲数字系统与FPGA设计概述 西安邮电学院通信工程系 可编程逻辑器件的发展概况 当今社会是数字化社会,数字集成电路应用非常广泛, 其发展从电子管、晶体管、SSI、MSI、LSI、VLSI到 ULSI,其规模几乎平均每18个月翻一番(摩尔定律)。 冬ASIC是专门为某一应用领域或某一专门用户需要而设 计制造的集成电路。特点:量产成本低,但开发周期长, 投入大,风险大,特别是到0.18微米后,投片费大增。 冬可编程逻辑器件PLD(Programmable Logic Device)是 从可编程逻辑阵列和ASIC中发展出来的新器件。特点: 开发周期短,设计修改灵活,无投片费,量产成本较高

第一讲 数字系统与FPGA设计概述 西安邮电学院通信工程系 ❖ 当今社会是数字化社会, 数字集成电路应用非常广泛, 其发展从电子管、 晶体管、SSI、 MSI、 LSI、VLSI到 ULSI, 其规模几乎平均每18个月翻一番(摩尔定律)。 ❖ ASIC 是专门为某一应用领域或某一专门用户需要而设 计制造的集成电路。特点:量产成本低,但开发周期长, 投入大,风险大,特别是到0.18微米后,投片费大增。 ❖ 可编程逻辑器件PLD(Programmable Logic Device)是 从可编程逻辑阵列和ASIC中发展出来的新器件。特点: 开发周期短,设计修改灵活,无投片费,量产成本较高。 可编程逻辑器件的发展概况

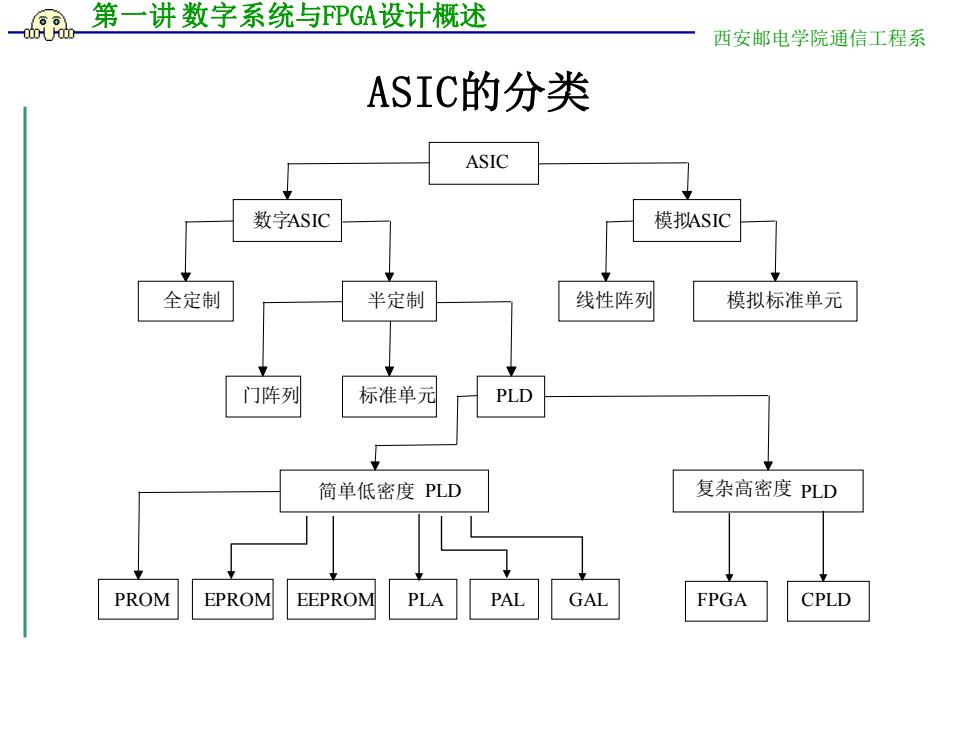

第一讲数字系统与FPGA设计概述 西安邮电学院通信工程系 ASIC的分类 ASIC 数字ASIC 模ASIC 全定制 半定制 线性阵列 模拟标准单元 门阵列 标准单元 PLD 简单低密度PLD 复杂高密度PLD PROM EPROM EEPROM PLA PAL GAL FPGA CPLD

第一讲 数字系统与FPGA设计概述 西安邮电学院通信工程系 ASIC的分类 PROM EPROM EEPROM PLA PAL GAL FPGA CPLD 简单低密度 PLD 复杂高密度 PLD 门阵列 标准单元 PLD 全定制 半定制 线性阵列 模拟标准单元 数字ASIC 模拟ASIC ASIC

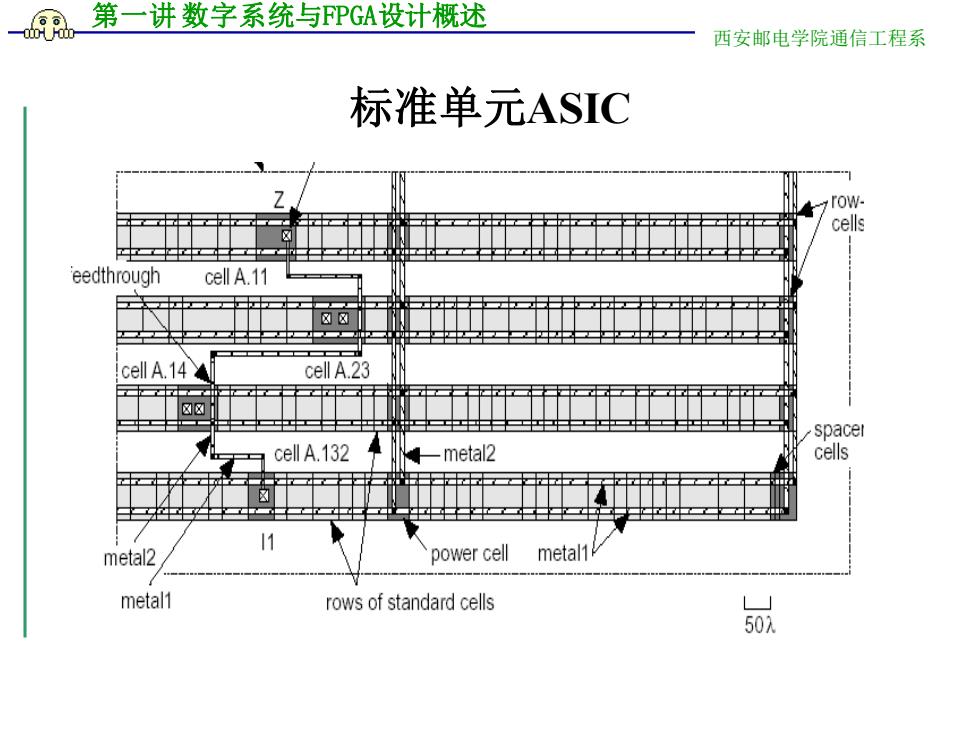

第一讲数字系统与FPGA设计概述 西安邮电学院通信工程系 标准单元ASIC roW- cells eedthrough cell A.11 ☒☒ cell A.14 cell A.23 ☒☒ spacer cell A.132 metal2 cells 11 metal2 power cell metal14 metal1 rows of standard cells L 501

第一讲 数字系统与FPGA设计概述 西安邮电学院通信工程系 标准单元ASIC

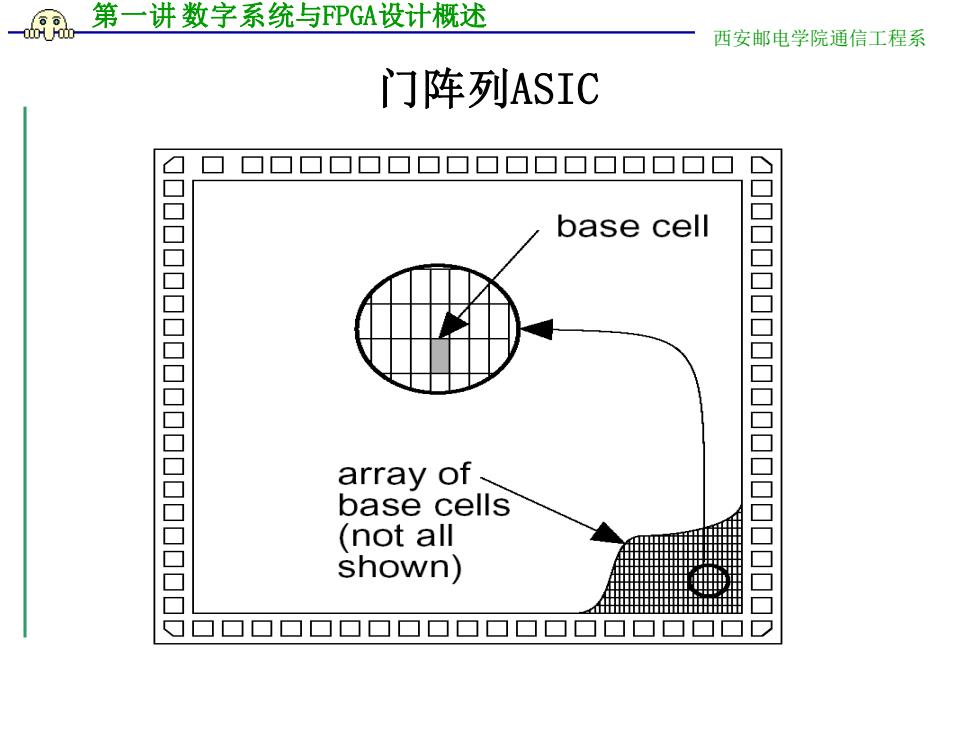

第一讲数字系统与FPGA设计概述 西安邮电学院通信工程系 门阵列ASIC 口口口口口口口口口口口口□□口口□ base cell 口 ▣ array of base cells (not all shown)

第一讲 数字系统与FPGA设计概述 西安邮电学院通信工程系 门阵列ASIC

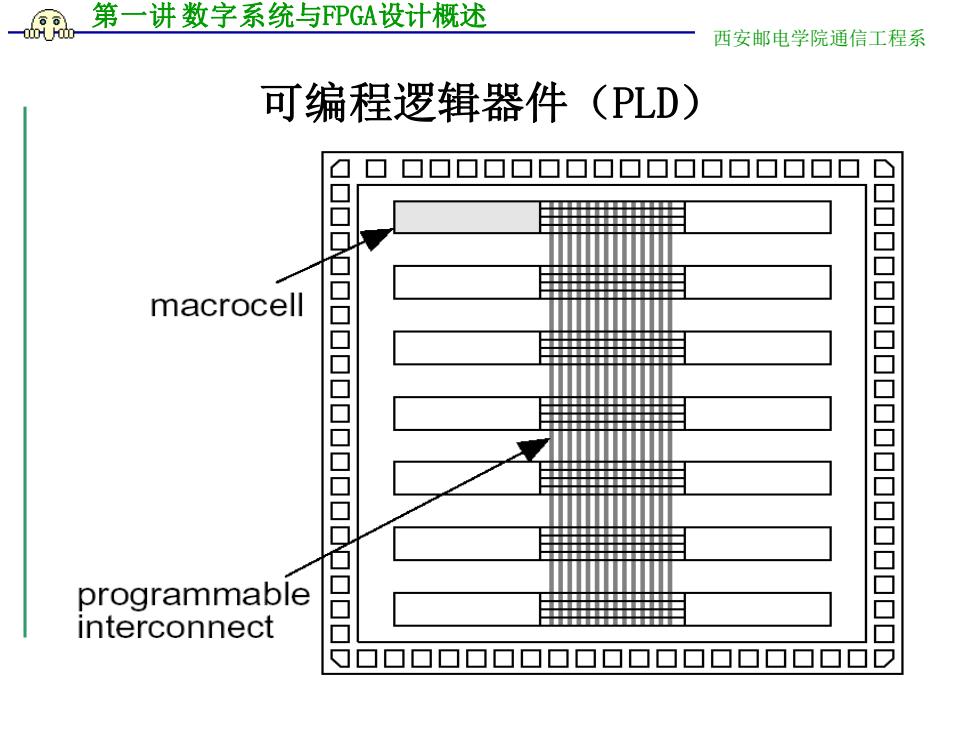

第一讲数字系统与FPGA设计概述 西安邮电学院通信工程系 可编程逻辑器件(PLD) macrocell 口口 programmable 口口 interconnect 口口 ▣口▣▣口▣口▣▣口▣口▣口口▣口口口口)

第一讲 数字系统与FPGA设计概述 西安邮电学院通信工程系 可编程逻辑器件(PLD)