第六讲数字系统级设计原则与设计实例 西安邮电学院通信工程系 不可靠门控时钟例 如图示门控时钟将不能正常工作,因RCO信号有毛刺。 DATA D OUT 8 RCO ENABLE EN CLK CLK QA c RCO 不希望 希望的时 的毛刺 钟上升沿

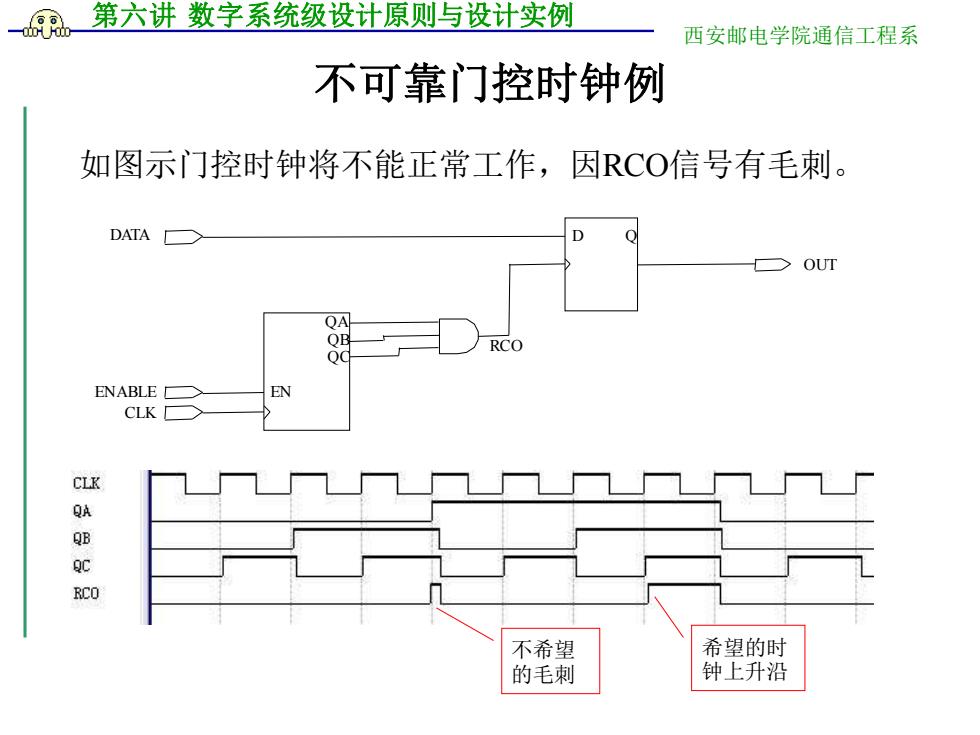

第六讲 数字系统级设计原则与设计实例 西安邮电学院通信工程系 不可靠门控时钟例 如图示门控时钟将不能正常工作,因RCO信号有毛刺。 D Q OUT QA QB QC EN CLK ENABLE RCO DATA 不希望 的毛刺 希望的时 钟上升沿

第六讲数字系统级设计原则与设计实例 西安邮电学院通信工程系 不可靠的门控时钟转换为全局时钟 DATA D PRN Q OUT ENA CLRN RCO 88 ENABLE EN 3位二进制 CLK 可逆计数器 使能的时钟上升 沿与原设计等效 K QA R00 作为使能信 号毛刺无影 响

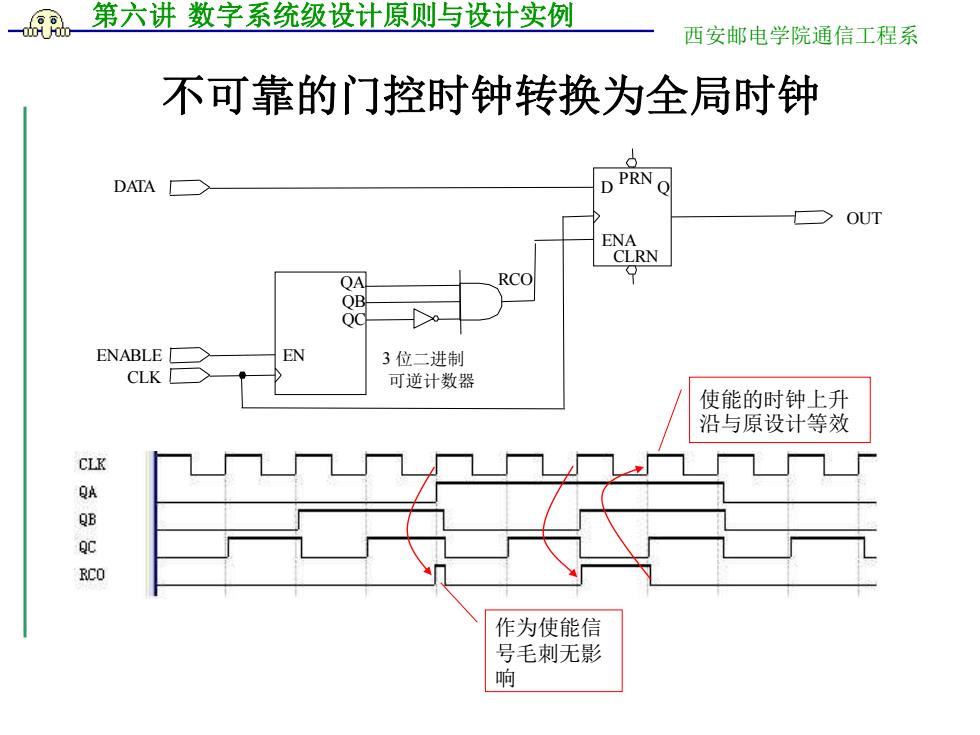

第六讲 数字系统级设计原则与设计实例 西安邮电学院通信工程系 不可靠的门控时钟转换为全局时钟 D Q PRN CLRN ENA OUT QA QB QC EN CLK ENABLE RCO DATA 3 位二进制 可逆计数器 使能的时钟上升 沿与原设计等效 作为使能信 号毛刺无影 响

第六讲数字系统级设计原则与设计实例 西安邮电学院通信工程系 行波时钟 所谓行波时钟是指一个触发器的输出用作另一个触发器的时钟输入。如果 仔细设计,行波时钟可以像全局时钟一样可靠工作,但是行波时钟使得 与电路有关的定时计算变得很复杂。行波时钟在行波链上各触发器时钟之 间产生较大的时间偏移,使系统的实际速度下降。同步数字系统设计中一 般只用全局时钟和门控时钟,不用行波时钟 冬用T触发器构成异步计数器时,常采用行波时钟,一个触发器的输出作为 时钟控制下一个触发器的输入,如下图: VCC ENABLE OUT CLK LRN CLRN CLRN ●

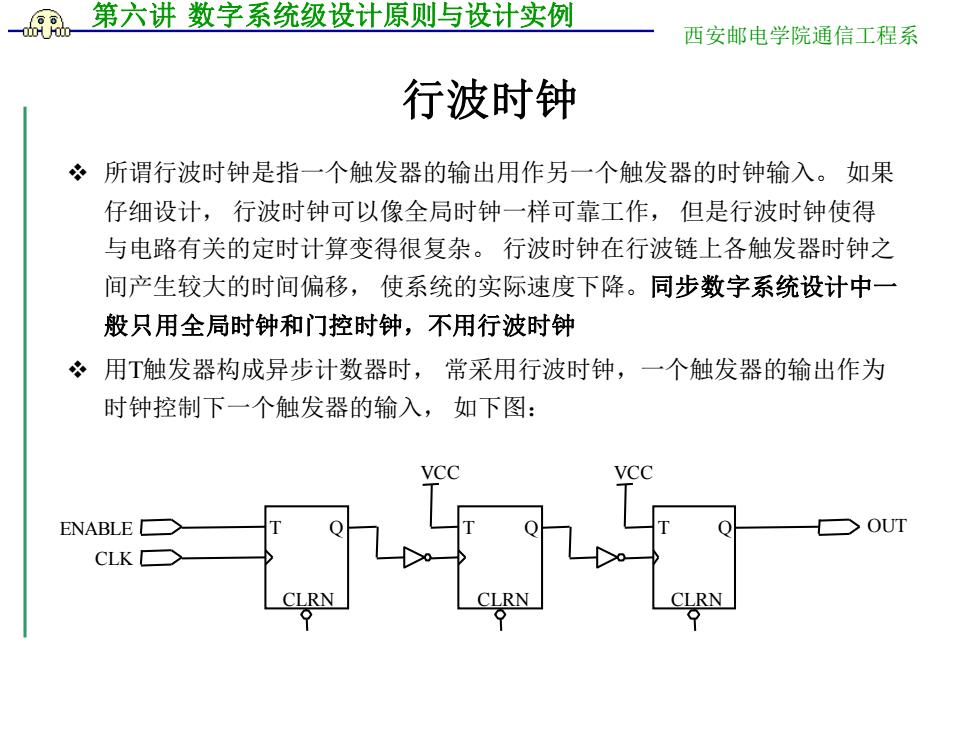

第六讲 数字系统级设计原则与设计实例 西安邮电学院通信工程系 行波时钟 ❖ 所谓行波时钟是指一个触发器的输出用作另一个触发器的时钟输入。 如果 仔细设计, 行波时钟可以像全局时钟一样可靠工作, 但是行波时钟使得 与电路有关的定时计算变得很复杂。 行波时钟在行波链上各触发器时钟之 间产生较大的时间偏移, 使系统的实际速度下降。同步数字系统设计中一 般只用全局时钟和门控时钟,不用行波时钟 ❖ 用T触发器构成异步计数器时, 常采用行波时钟,一个触发器的输出作为 时钟控制下一个触发器的输入, 如下图: CLK T Q CLRN T Q CLRN T Q CLRN ENABLE VCC VCC OUT

第六讲数字系统级设计原则与设计实例 西安邮电学院通信工程系 多时钟域系统 冬许多系统要求在同一设计内采用多时钟,每个时钟驱动的触发器 集合称为一个时钟域。最常见的例子是两个异步微处理器之间的 接口,或微处理器和异步通信通道的接口。 ?在同步逻辑电路的系统中,如果存在两个时钟域或异步输入,对 属于其它时钟域的信号,在输入CLK2域时需要和CLK2同步。同 步方式与时钟频率有关。 CLK2时 CLKI时 异步 钟域 钟域 接口 CLKI CLK2

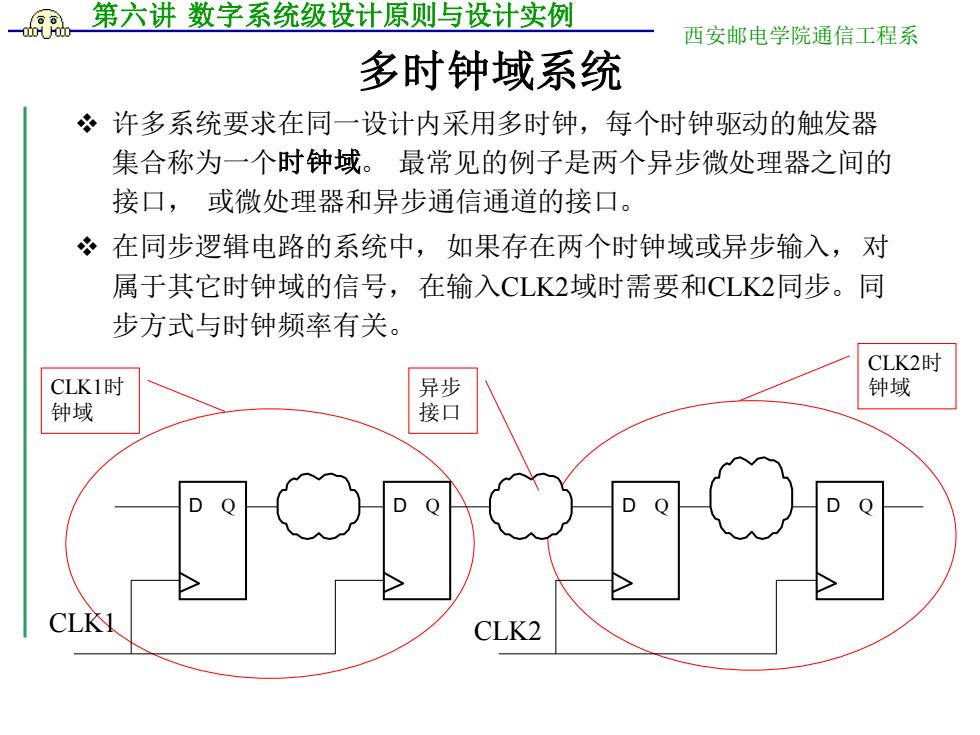

第六讲 数字系统级设计原则与设计实例 西安邮电学院通信工程系 多时钟域系统 ❖ 许多系统要求在同一设计内采用多时钟,每个时钟驱动的触发器 集合称为一个时钟域。 最常见的例子是两个异步微处理器之间的 接口, 或微处理器和异步通信通道的接口。 ❖ 在同步逻辑电路的系统中,如果存在两个时钟域或异步输入,对 属于其它时钟域的信号,在输入CLK2域时需要和CLK2同步。同 步方式与时钟频率有关。 D Q CLK1 CLK2 D Q D Q D Q CLK1时 钟域 CLK2时 异步 钟域 接口

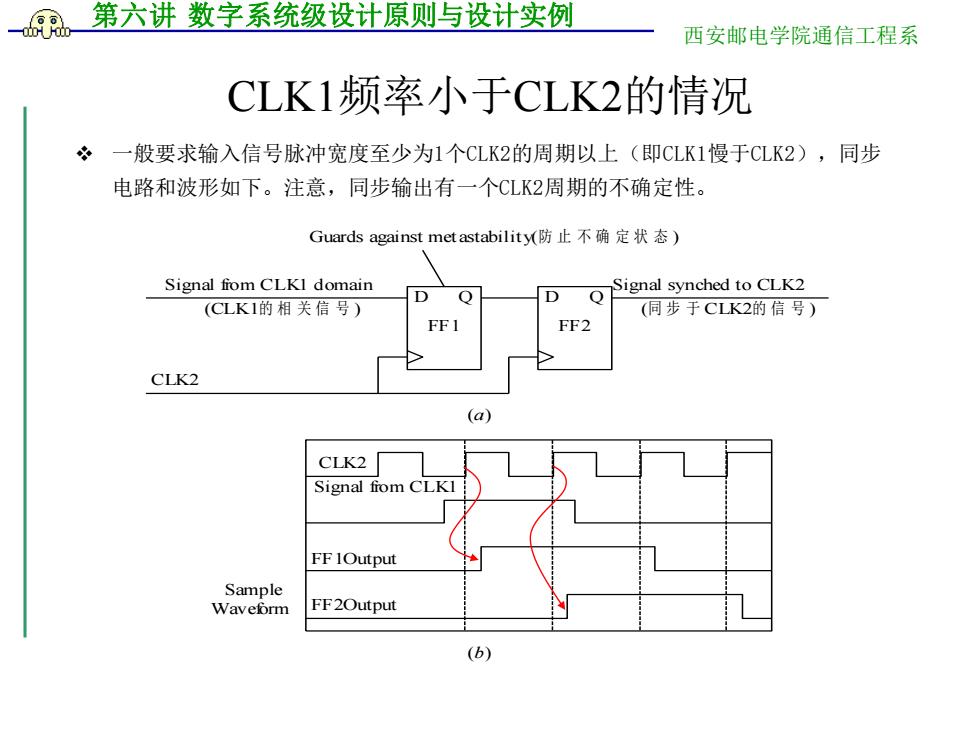

第六讲数字系统级设计原则与设计实例 西安邮电学院通信工程系 CLK1频率小于CLK2的情况 ,一般要求输入信号脉冲宽度至少为1个CLK2的周期以上(即CLK1慢于CLK2),同步 电路和波形如下。注意,同步输出有一个CLK2周期的不确定性。 Guards against met astability(防止不确定状态) Signal firom CLKI domain Signal synched to CLK2 D (CLK1的相关信号) (同步于CLK2的信号) FF1 FF2 CLK2 (a) CLK2 Signal fiom CLKI FF 1Output Sample Wavefrm FF2Output (b)

第六讲 数字系统级设计原则与设计实例 西安邮电学院通信工程系 CLK1频率小于CLK2的情况 ❖ 一般要求输入信号脉冲宽度至少为1个CLK2的周期以上(即CLK1慢于CLK2),同步 电路和波形如下。注意,同步输出有一个CLK2周期的不确定性。 FF2 D Q FF1 D Q Signal synched to CLK2 (同 步 于 CLK2的 信 号 ) Signal from CLK1 domain (CLK1的 相 关 信 号 ) CLK2 Guards against metastability(防 止 不 确 定 状 态 ) (a) CLK2 Signal from CLK1 FF1Output FF2Output Sample Waveform (b)