第六讲数字系统级设计原则与设计实例 西安邮电学院通信工程系 同步设计原则 早期的C设计常用异步设计,如行波计数器和异步脉冲发生器等, 以减少设计面积。 ?异步设计时序控制相当繁杂而困难,且目前EDA工具多不支持异 步设计,较大规模的异步设计十分费时费力。 随着C技术发展,减少器件资源已不是主要问题,设计的稳定可 靠、与工艺无关,减少设计周期更为重要。 。因此同步设计是目前C设计的重要原则之一。 冬同步系统设计中的基本问题: 设计必须满足同步触发器的建立、保持时间。 同步系统时钟、复位的合理规划。 ·注意同步时钟域间信号的转换

第六讲 数字系统级设计原则与设计实例 西安邮电学院通信工程系 同步设计原则 ❖ 早期的IC设计常用异步设计,如行波计数器和异步脉冲发生器等, 以减少设计面积。 ❖ 异步设计时序控制相当繁杂而困难,且目前EDA工具多不支持异 步设计,较大规模的异步设计十分费时费力。 ❖ 随着IC技术发展,减少器件资源已不是主要问题,设计的稳定可 靠、与工艺无关,减少设计周期更为重要。 ❖ 因此同步设计是目前IC设计的重要原则之一。 ❖ 同步系统设计中的基本问题: ▪ 设计必须满足同步触发器的建立、保持时间。 ▪ 同步系统时钟、复位的合理规划。 ▪ 注意同步时钟域间信号的转换

第六讲数字系统级设计原则与设计实例 西安邮电学院通信工程系 同步系统时钟的规划 。在同步数字系统设计中,设计不良的时钟将导致系统 错误的行为,特别是在温度、电压或制造工艺存在偏 差的情况下,很容易出现问题,所以可靠的时钟规划 设计是非常关键的。在数字逻辑设计时通常有以下三 种时钟方式: 全局时钟 门控时钟 行波时钟

第六讲 数字系统级设计原则与设计实例 西安邮电学院通信工程系 同步系统时钟的规划 ❖ 在同步数字系统设计中,设计不良的时钟将导致系统 错误的行为,特别是在温度、电压或制造工艺存在偏 差的情况下,很容易出现问题,所以可靠的时钟规划 设计是非常关键的。 在数字逻辑设计时通常有以下三 种时钟方式: ▪ 全局时钟 ▪ 门控时钟 ▪ 行波时钟

第六讲数字系统级设计原则与设计实例 西安邮电学院通信工程系 全局时钟 冬对于一个同步数字系统设计项目来说,全局时钟是最 简单和可预测的时钟。 文 在FPGA设计中最好的时钟方案是: 由专用的全局 时钟输入引脚驱动单个主时钟去控制设计项目中的每 一个触发器。 FPGA一般都具有专门的全局时钟引脚,在设计项目 时应尽量采用全局时钟,它能够提供器件中最短的时 钟到输出的延时和时钟偏移

第六讲 数字系统级设计原则与设计实例 西安邮电学院通信工程系 全局时钟 ❖ 对于一个同步数字系统设计项目来说, 全局时钟是最 简单和可预测的时钟。 ❖ 在FPGA设计中最好的时钟方案是: 由专用的全局 时钟输入引脚驱动单个主时钟去控制设计项目中的每 一个触发器。 ❖ FPGA一般都具有专门的全局时钟引脚, 在设计项目 时应尽量采用全局时钟, 它能够提供器件中最短的时 钟到输出的延时和时钟偏移

第六讲数字系统级设计原则与设计实例 西安邮电学院通信工程系 时钟偏移 冬时序电路在FPGA中实现时,若不用全局时钟,由于时钟各部分连线长 短不一致,虽然多个触发器共用一个时钟信号, 但触发器时钟端的信号 延时并不相同,信号会发生不同的畸变,构成时钟信号偏移。 Din CLK A B (a) A&C CLK B QB Expected operation Clock skewed version Q C (b) (c)

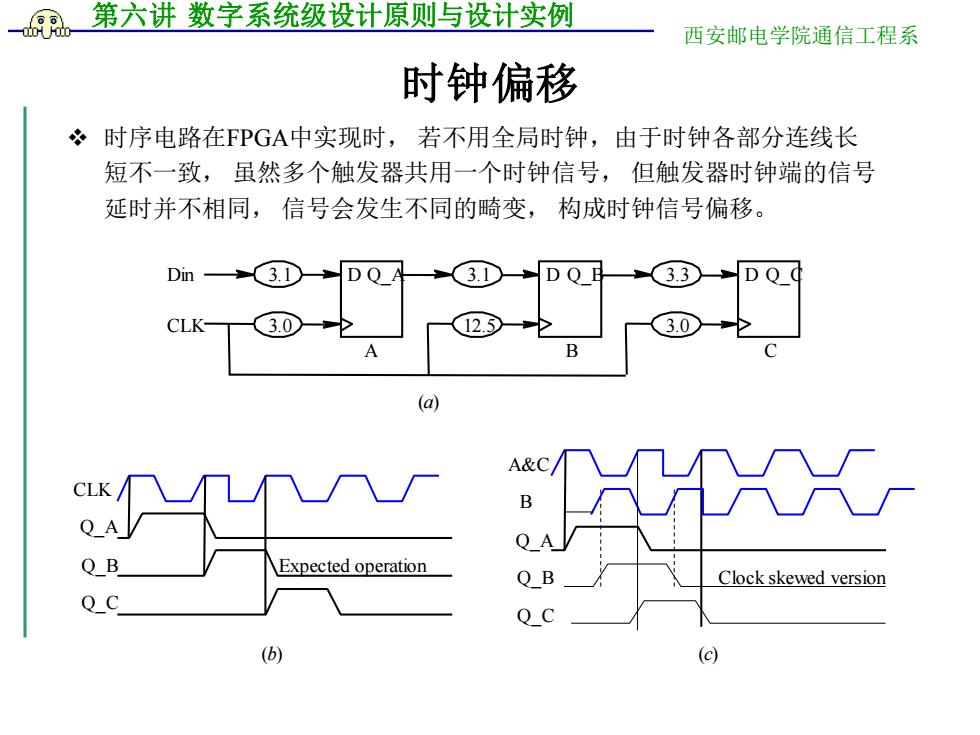

第六讲 数字系统级设计原则与设计实例 西安邮电学院通信工程系 时钟偏移 ❖ 时序电路在FPGA中实现时, 若不用全局时钟,由于时钟各部分连线长 短不一致, 虽然多个触发器共用一个时钟信号, 但触发器时钟端的信号 延时并不相同, 信号会发生不同的畸变, 构成时钟信号偏移。 D Q_A A 3.0 3.1 CLK Din D Q_B B 12.5 3.1 D Q_C C 3.0 3.3 (a) Expected operation CLK Q_A Q_B Q_C (b) Clock skewed version A&C Q_A Q_B Q_C (c) B

第六讲数字系统级设计原则与设计实例 西安邮电学院通信工程系 门控时钟 在许多应用中, 整个设计项目都采用外部的全局时钟是不可能或不实际 的,所以通常用控制逻辑门和时钟构成门控时钟。门控时钟常常同微 处理器接口有关,例如用地址线去控制写脉冲。 DI 时钟 与门控 组合逻辑 制逻辑 Dn D PRN Q nWR OUT ADDO CLRN ADDI 门控时钟nWR必 ADD2 门控 须保证无毛刺, ADD3 信号 且门控信号ADD 在触发器的建立 改变 稳定 改变 D(n.1] 保持时间窗和 +su一h+ nWR为0时期内 nWR 保证信号稳定。 ADD[3.0] 改变 稳定

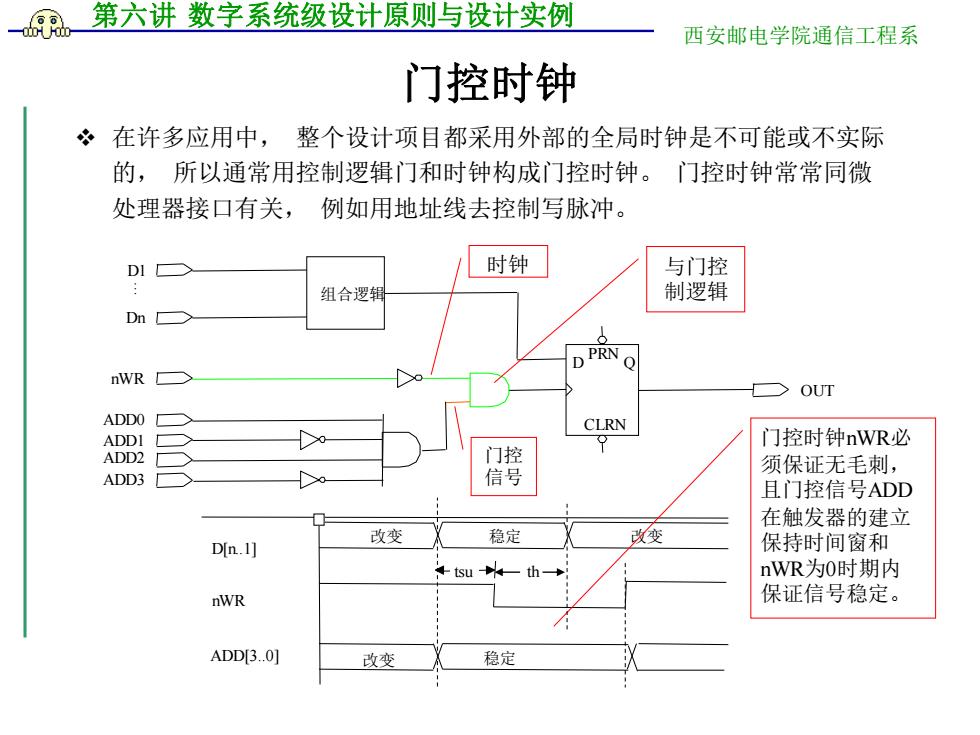

第六讲 数字系统级设计原则与设计实例 西安邮电学院通信工程系 门控时钟 ❖ 在许多应用中, 整个设计项目都采用外部的全局时钟是不可能或不实际 的, 所以通常用控制逻辑门和时钟构成门控时钟。 门控时钟常常同微 处理器接口有关, 例如用地址线去控制写脉冲。 改变 稳定 改变 改变 稳定 D[n.1] nWR ADD[3.0] tsu th D Q PRN CLRN 组合逻辑 D1 . Dn OUT nWR ADD0 ADD1 ADD2 ADD3 门控时钟nWR必 须保证无毛刺, 且门控信号ADD 在触发器的建立 保持时间窗和 nWR为0时期内 保证信号稳定。 时钟 门控 信号 与门控 制逻辑