西安邮电大学通信基础实验教学中心 Simuink Library Browser file Edit View Simulation Format Tools Help D日0第t2■0.0r1 8 ☑ 国 四 四 网 ode45 双击刚刚拖拽进来的System Generator图标进行参数设置。 l)在Compilation下。Compilation处选择生成Bitstream,以便直 接下载调试;Part处选择所使用的FPGA型号,由于我们的板 子是Nexys3,所以选择Spartane6xc6sx16-3csg324。其他选择 默认即可。 System Generator:untitled ▣回x Compilation Clocking General Compilation: ②Bitstream Settings,. Part: Spartan6 xc6s16-3csg324 Synthesis tool Hardware description language XST VHDL Target directory: /netlist Browse. Project type: Project Navigator Synthesis strategy Implementation strategy XST Defaults* ISE Defaults" Create interface document 圆Create testbench Import as configurable subsystem Performance Tips Generate OK Apply Cancel Help 11/45

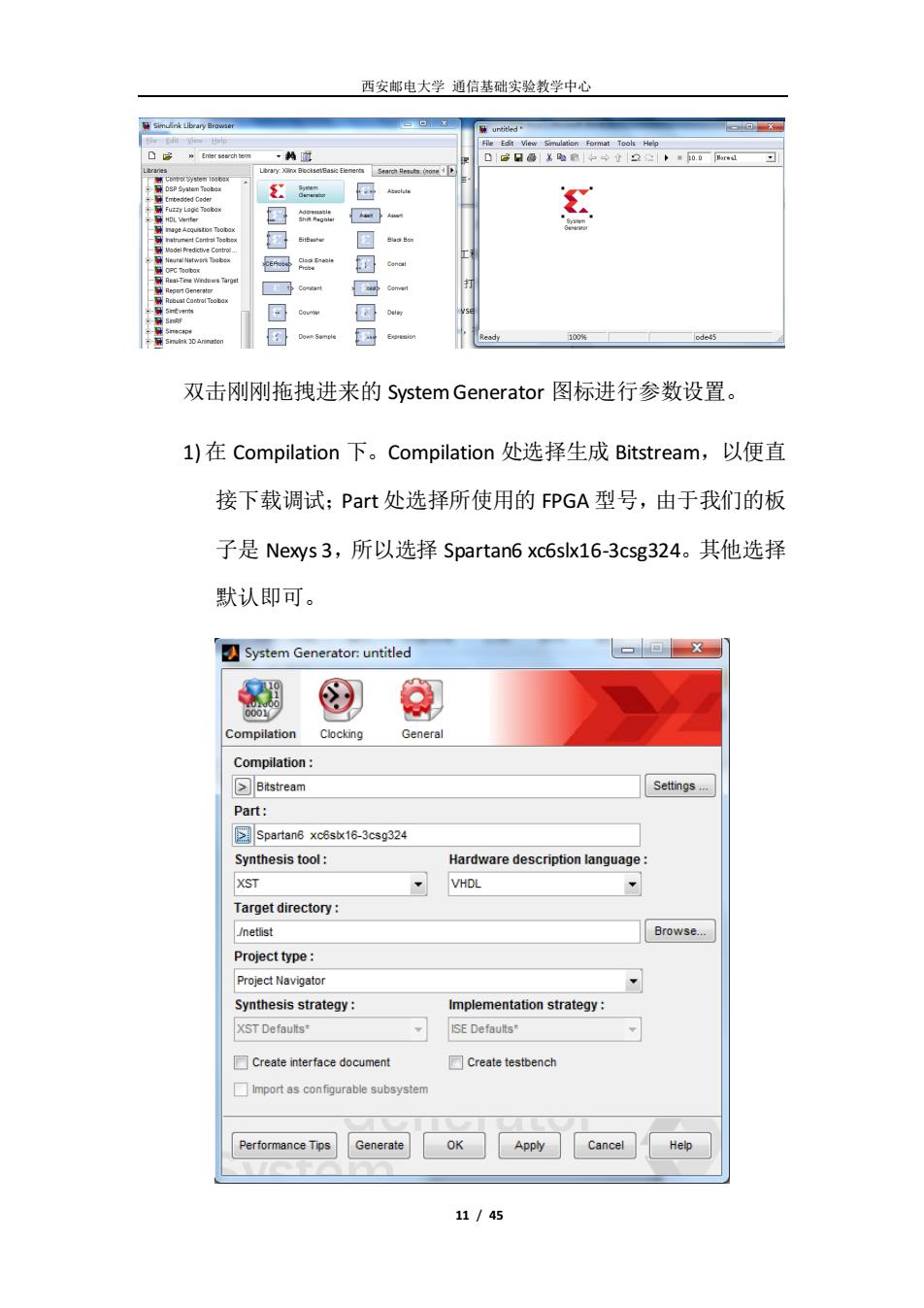

西安邮电大学 通信基础实验教学中心 11 / 45 双击刚刚拖拽进来的 System Generator 图标进行参数设置。 1) 在 Compilation 下。Compilation 处选择生成 Bitstream,以便直 接下载调试;Part 处选择所使用的 FPGA 型号,由于我们的板 子是 Nexys 3,所以选择 Spartan6 xc6slx16-3csg324。其他选择 默认即可

西安邮电大学通信基础实验教学中心 2)在Clocking下。Nexys3的系统时钟为100MHz,周期10ns,引 脚为VI0,因此,FPGA clock period(ns)处按默认的10不变, Clock pin location处输入V10. System Generator:untitled 回 0001 Compilation Clocking General FPGA clock period(ns): Clock pin location: 10 V10 Multirate implementation DCM input clock period(ns): Clock Enables 10 Provide clock enable clear pin Simulink system period(sec): 1 Performance Tips Generate OK Apply Cancel Help 3)General下按照默认设置即可。 以上工作都完成以后,点击下方的OK按钮退出该界面。 12/45

西安邮电大学 通信基础实验教学中心 12 / 45 2) 在 Clocking 下。Nexys 3 的系统时钟为 100MHz,周期 10ns,引 脚为 V10,因此,FPGA clock period(ns)处按默认的 10 不变, Clock pin location 处输入 V10。 3) General 下按照默认设置即可。 以上工作都完成以后,点击下方的 OK 按钮退出该界面

西安邮电大学通信基础实验教学中心 2.3主要模块设计 2.3.1AD时序设计 由AD芯片的引脚功能可知,其与FPGA之间进行通信的引脚有 三个:SCK、SDATA、/CS。通常情况下,我们采用设置采样周期(Sample period或Explicit period)来确定信号的时序。 1)SCLK。时钟信号的建立采用计数器Counter来实现,由于AD 转换芯片ADC081S021的时钟频率为25KHz一20MHz,此处 我们定义该时钟为100KHz。通过计算公式来确定采样周期 此处的Simulink system period的设置是在System Generator图标下。如下图所示: 13/45

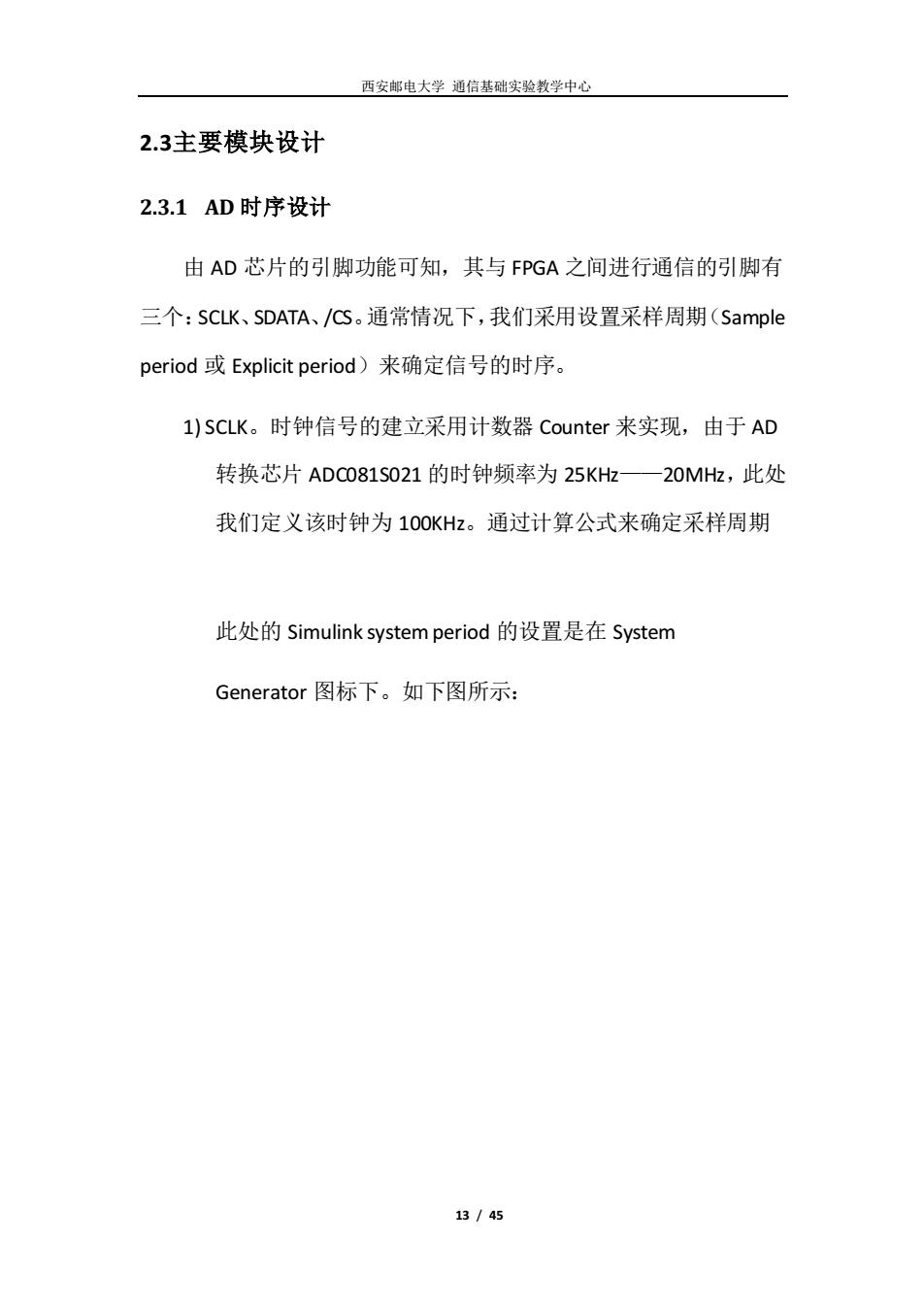

西安邮电大学 通信基础实验教学中心 13 / 45 2.3主要模块设计 2.3.1 AD 时序设计 由 AD 芯片的引脚功能可知,其与 FPGA 之间进行通信的引脚有 三个:SCLK、SDATA、/CS。通常情况下,我们采用设置采样周期(Sample period 或 Explicit period)来确定信号的时序。 1) SCLK。时钟信号的建立采用计数器 Counter 来实现,由于 AD 转换芯片 ADC081S021 的时钟频率为 25KHz——20MHz,此处 我们定义该时钟为 100KHz。通过计算公式来确定采样周期 此处的 Simulink system period 的设置是在 System Generator 图标下。如下图所示:

西安邮电大学通信基础实验教学中心 System Generator:tiaozhi_stephen ▣回X Compilation Clocking General FPGA clock period(ns): Clock pin location: /10 V10 Multirate implementation: DCM input clock period(ns): Clock Enables 10 Provide clock enable clear pin Simulink system period(sec): Performance Tips Generate OK Apply Cancel Help 由以上计算公式带入数据,可以得到计数器的Explicit period 为500,由于此信号是时钟信号,计数器循环的在0和1之 间进行变动。见下图: 14/45

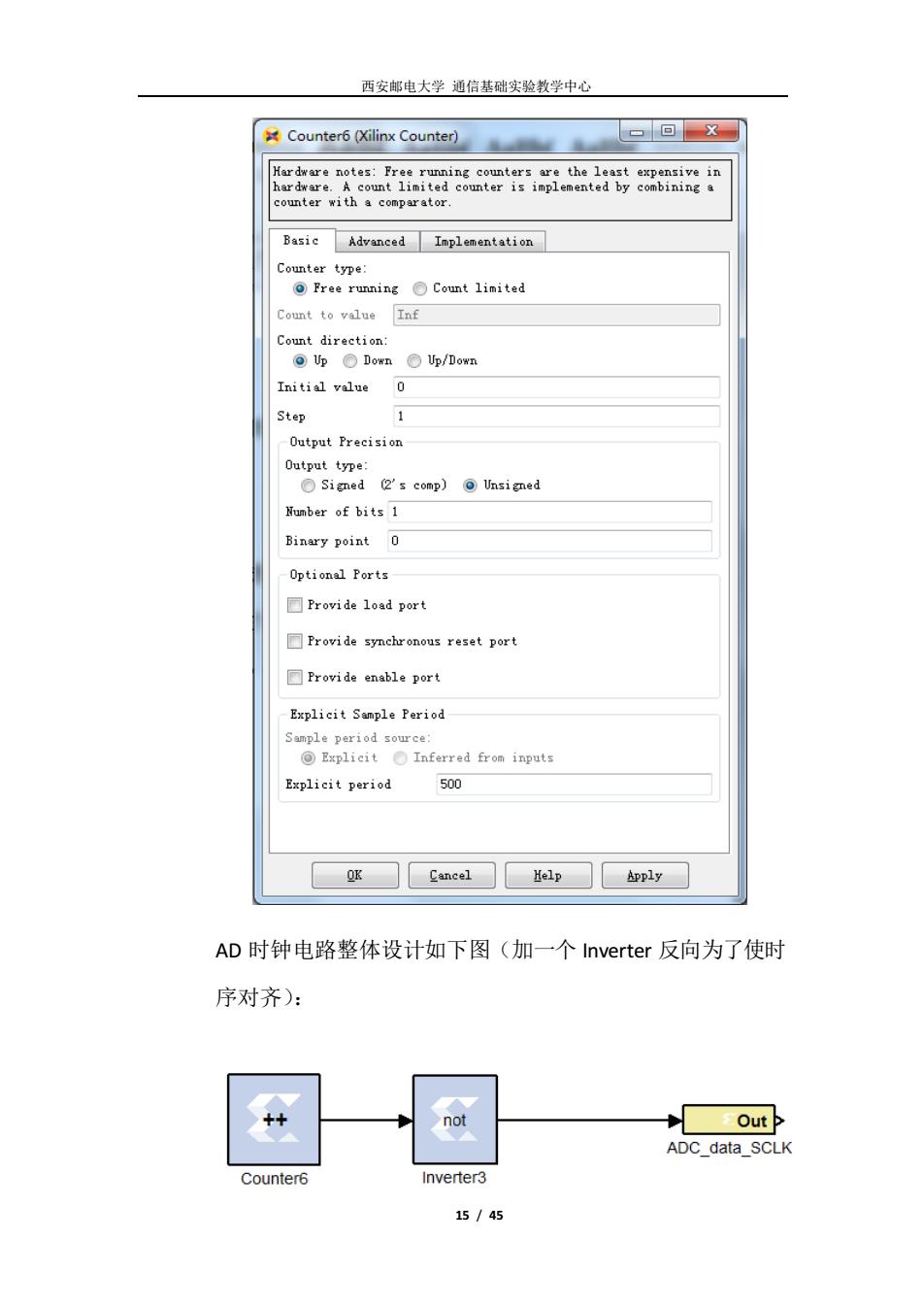

西安邮电大学 通信基础实验教学中心 14 / 45 由以上计算公式带入数据,可以得到计数器的 Explicit period 为 500,由于此信号是时钟信号,计数器循环的在 0 和 1 之 间进行变动。见下图:

西安邮电大学通信基础实验教学中心 Counter6(Xilinx Counter) ▣回X Hardware notes:Free running counters are the least expensive in hardware.A count limited counter is implemented by combining a counter with a comparator. Basic Advanced Implementation Counter type: ⊙Free running©Count limited Count to value Inf Count direction ⊙Up○Down○p/Down Initial value 0 Step 2 Output Precision Output type: Siged (2's comp) 6 Unsiged Number of bits 1 Binary point 0 Optional Ports □Provide1 oad port Provide synchronous reset port □Provide enable port Explicit Sample Period Sample period source: Explicit Inferred from inputs Explicit period 500 OK Cancel Help Apply AD时钟电路整体设计如下图(加一个Inverter反向为了使时 序对齐): not Out ADC data SCLK Counter6 Inverter3 15/45

西安邮电大学 通信基础实验教学中心 15 / 45 AD 时钟电路整体设计如下图(加一个 Inverter 反向为了使时 序对齐):