西安邮电大学通信基础实验教学中心 1.2DA芯片的型号及时序 本综合实验系统的ADC DAC扩展卡上搭载了4路DA采样电路。 所选用的DA芯片是T1公司的8位微功耗轨到轨数模转换器 DAC081S101。 DAC081S101是一种全功能、通用的8位电压输出的数模转换器, 它可以在+2.7V一+5.5V单端电源下工作,并且在3.6V电压下仅仅消耗 175uA电流。 DAC081S101的引脚图如下: VOUT SYNC GND- 2 5 SCLK VA- 3 -DIN 引脚描述 符号 引脚号 描述 VOUT 1 DAC模拟输出电压 GND 2 对于所有电路的接地参考 VA 3 电源和参考输入。需解耦至GND 6145

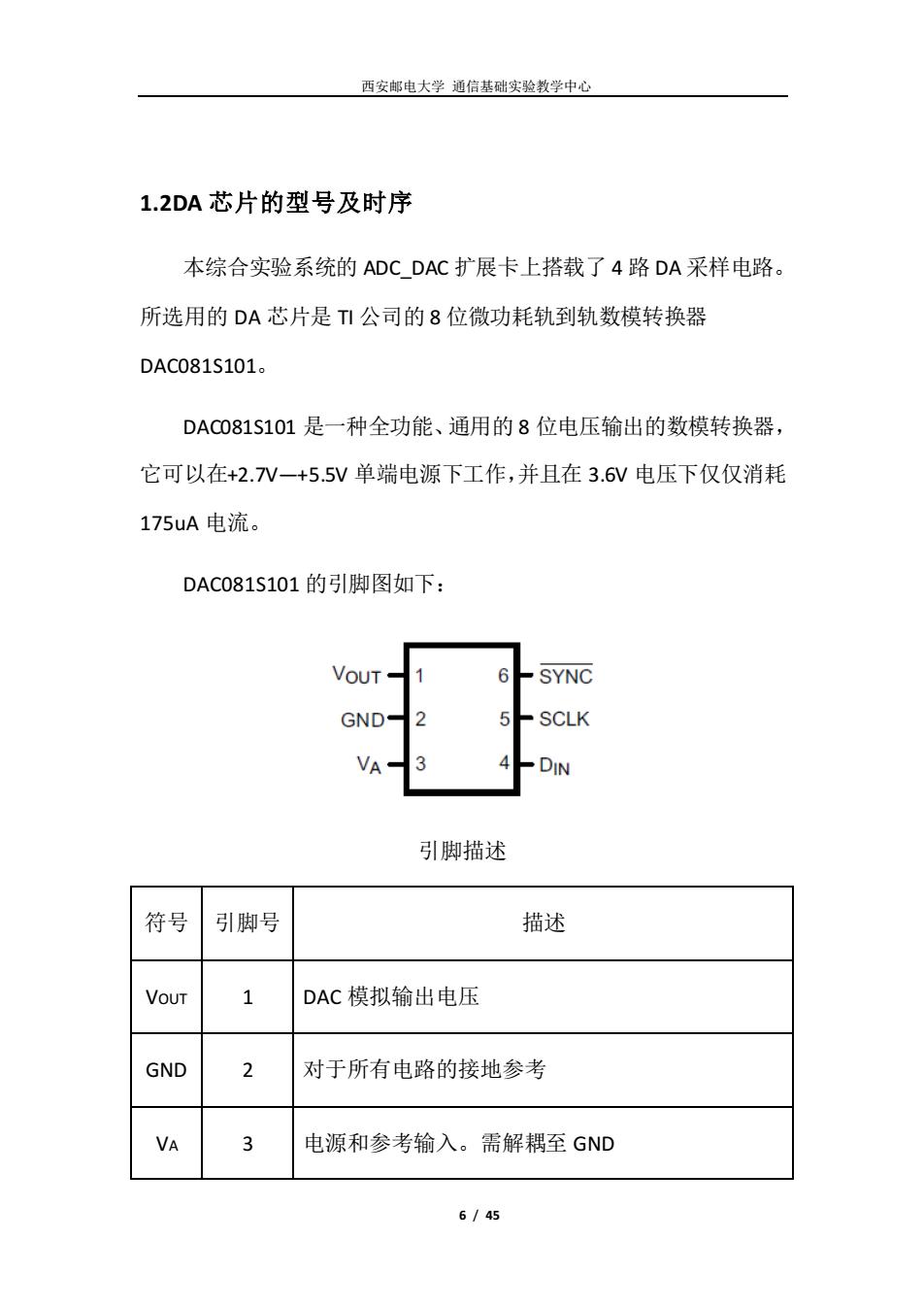

西安邮电大学 通信基础实验教学中心 6 / 45 1.2DA 芯片的型号及时序 本综合实验系统的 ADC_DAC 扩展卡上搭载了 4 路 DA 采样电路。 所选用的 DA 芯片是 TI 公司的 8 位微功耗轨到轨数模转换器 DAC081S101。 DAC081S101 是一种全功能、通用的 8 位电压输出的数模转换器, 它可以在+2.7V—+5.5V 单端电源下工作,并且在 3.6V 电压下仅仅消耗 175uA 电流。 DAC081S101 的引脚图如下: 引脚描述 符号 引脚号 描述 VOUT 1 DAC 模拟输出电压 GND 2 对于所有电路的接地参考 VA 3 电源和参考输入。需解耦至 GND

西安邮电大学通信基础实验教学中心 DIN 4 串行数据输入。在/SYNC信号下降以后,在SCLK信 号的下降沿,数据被输入16位移位寄存器。 SCLK 5 串行时钟输入。在此信号的下降沿,数据被拍入输 入移位寄存器 /SYNC 6 数据输入的帧同步输入。当此脚信号拉低,它使能 输入移位寄存器,数据在SCK的下降沿被转移。DAC 在第16个时钟周期被更新,除非/SYNC信号在第16 个时钟前被拉高,在这种情况下/SYNC的上升沿作 为一个中断,写序列被DAC忽略。 工作额定值如下: 工作温度范围 -40C≤TA≤+105C 电源电压,Va +2.7Vto5.5V 任意输入电压 -0.1Vto(VA+0.1V) 输出负载 0 to 1500 pF SCLK频率 Up to 30 MHz DAC081S101时序图: 7/45

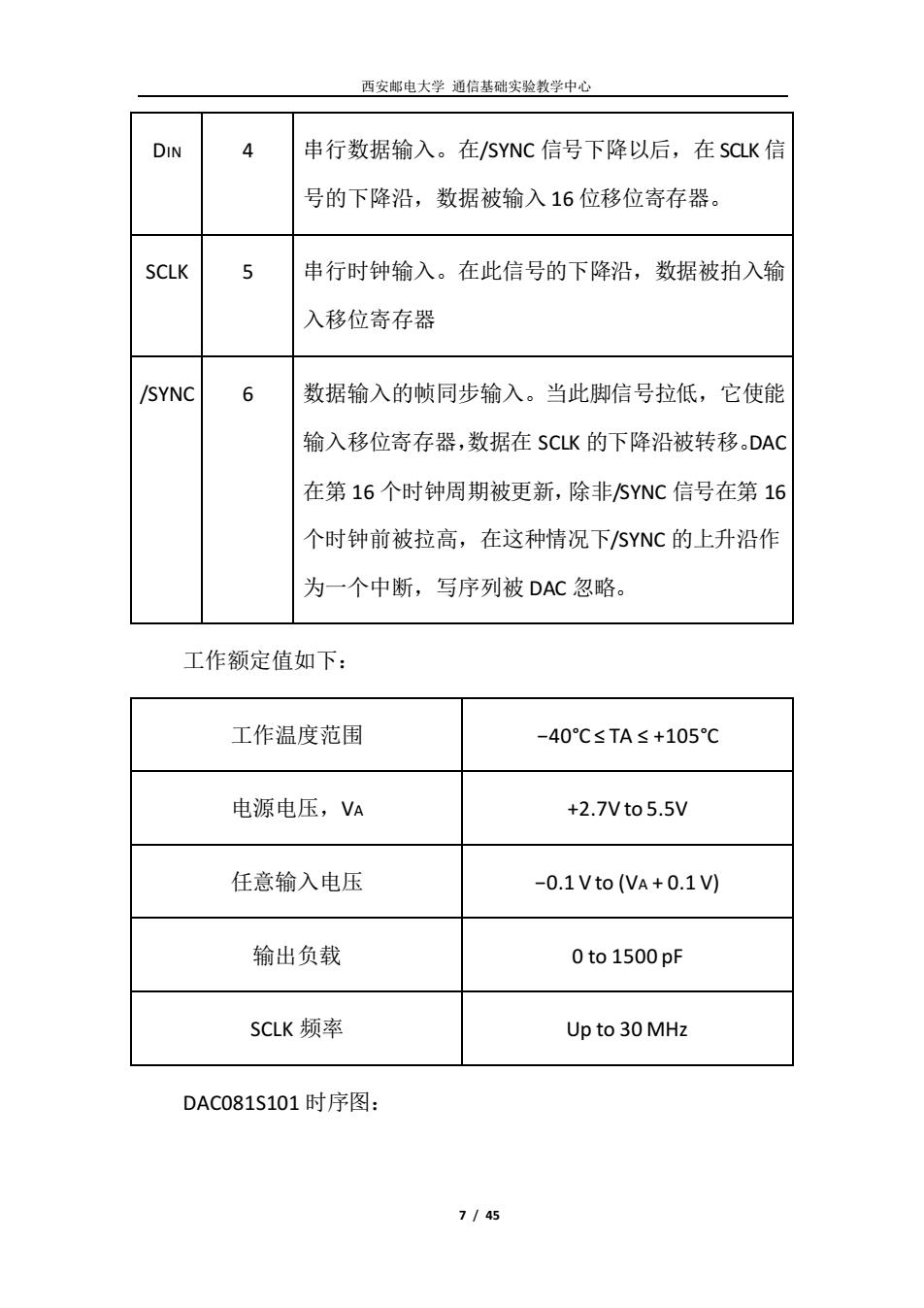

西安邮电大学 通信基础实验教学中心 7 / 45 DIN 4 串行数据输入。在/SYNC 信号下降以后,在 SCLK 信 号的下降沿,数据被输入 16 位移位寄存器。 SCLK 5 串行时钟输入。在此信号的下降沿,数据被拍入输 入移位寄存器 /SYNC 6 数据输入的帧同步输入。当此脚信号拉低,它使能 输入移位寄存器,数据在 SCLK 的下降沿被转移。DAC 在第 16 个时钟周期被更新,除非/SYNC 信号在第 16 个时钟前被拉高,在这种情况下/SYNC 的上升沿作 为一个中断,写序列被 DAC 忽略。 工作额定值如下: 工作温度范围 −40°C ≤ TA ≤ +105°C 电源电压,VA +2.7V to 5.5V 任意输入电压 −0.1 V to (VA + 0.1 V) 输出负载 0 to 1500 pF SCLK 频率 Up to 30 MHz DAC081S101 时序图:

西安邮电大学通信基础实验教学中心 SYNC DN 输入移位寄存器: 输入移位寄存器有16位。前2位是“无关”位,接下来的2位 决定了器件的工作模式,串行输入寄存器的内容在SCLK的第16个下 降沿转移到DAC寄存器。 输入寄存器的内容如下: MSB LSB xX PD1PD0 D7 D6 D5 D4 2D1 DATA BITS 00 Normal Operation 0 1 1 ko to GND 1 0 100 k to GND Power-Down Modes 1 1 High Impedance 正常情况下,/SYNC信号保持低电平至少到SCLK信号的16个下 降沿,同时,DAC在SCK信号的第16个下降沿进行更新。然而,如 果/SYNC信号在SCLK信号的第16个下降沿之前拉高,移位寄存器被 复位且写序列无效。DAC寄存器不会被更新,工作模式或者输出电压 没有改变。 8/45

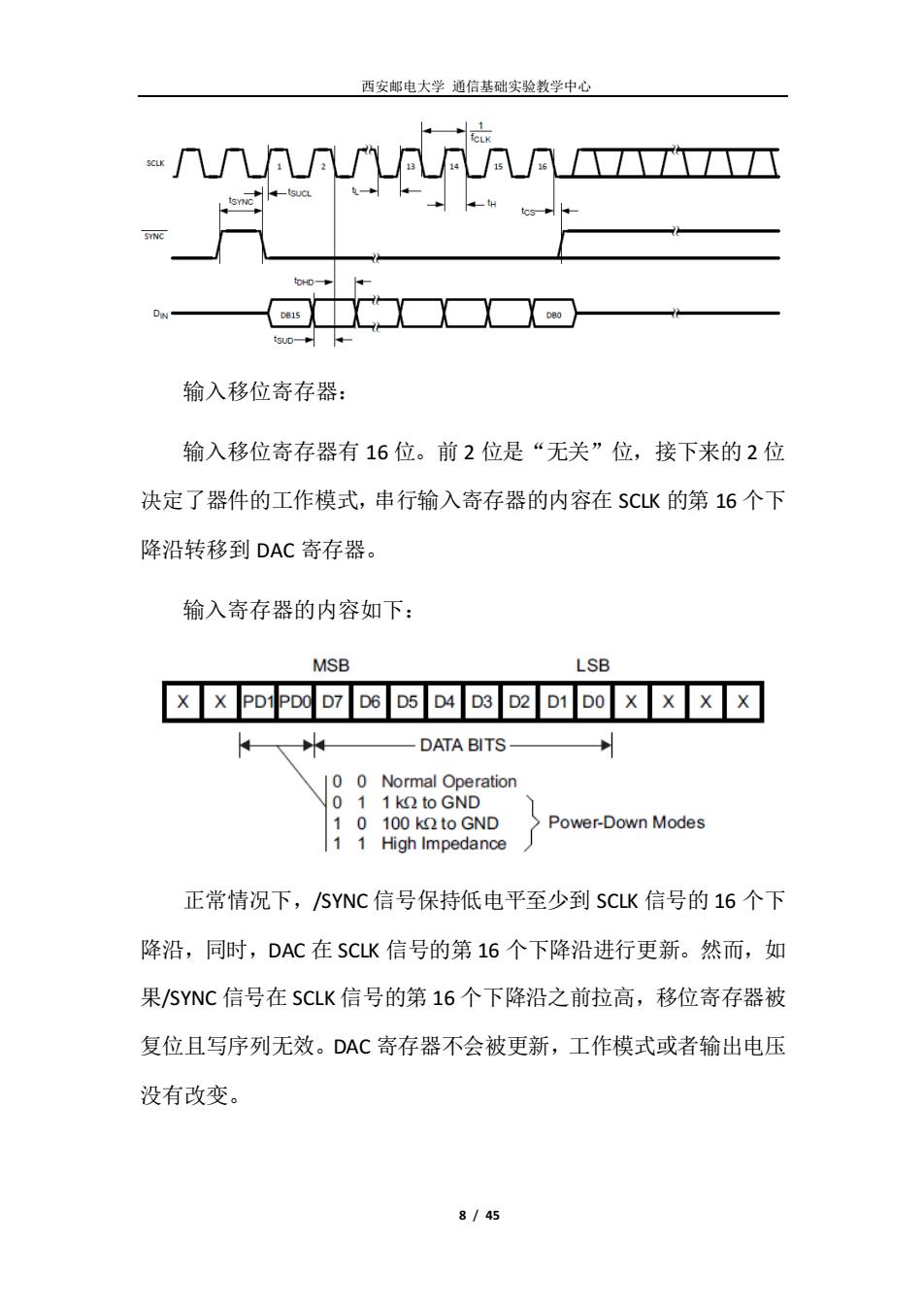

西安邮电大学 通信基础实验教学中心 8 / 45 输入移位寄存器: 输入移位寄存器有 16 位。前 2 位是“无关”位,接下来的 2 位 决定了器件的工作模式,串行输入寄存器的内容在 SCLK 的第 16 个下 降沿转移到 DAC 寄存器。 输入寄存器的内容如下: 正常情况下,/SYNC 信号保持低电平至少到 SCLK 信号的 16 个下 降沿,同时,DAC 在 SCLK 信号的第 16 个下降沿进行更新。然而,如 果/SYNC 信号在 SCLK 信号的第 16 个下降沿之前拉高,移位寄存器被 复位且写序列无效。DAC 寄存器不会被更新,工作模式或者输出电压 没有改变

西安邮电大学通信基础实验教学中心 在System Generator的设计中,为了满足信号输出时经过并串转 换后的时序要求,对DA部分的DN信号采取了组数操作,即在并串 转换前的8位数据高位添加4位0,低位添加20位0,同时/SYNC信 号保持低电平到SCLK信号的第32个下降沿。 欲了解该器件的详细信息,请查阅dac081s101.pdf文档。 9/45

西安邮电大学 通信基础实验教学中心 9 / 45 在 System Generator 的设计中,为了满足信号输出时经过并串转 换后的时序要求,对 DA 部分的 DIN 信号采取了组数操作,即在并串 转换前的 8 位数据高位添加 4 位 0,低位添加 20 位 0,同时/SYNC 信 号保持低电平到 SCLK 信号的第 32 个下降沿。 欲了解该器件的详细信息,请查阅 dac081s101.pdf 文档

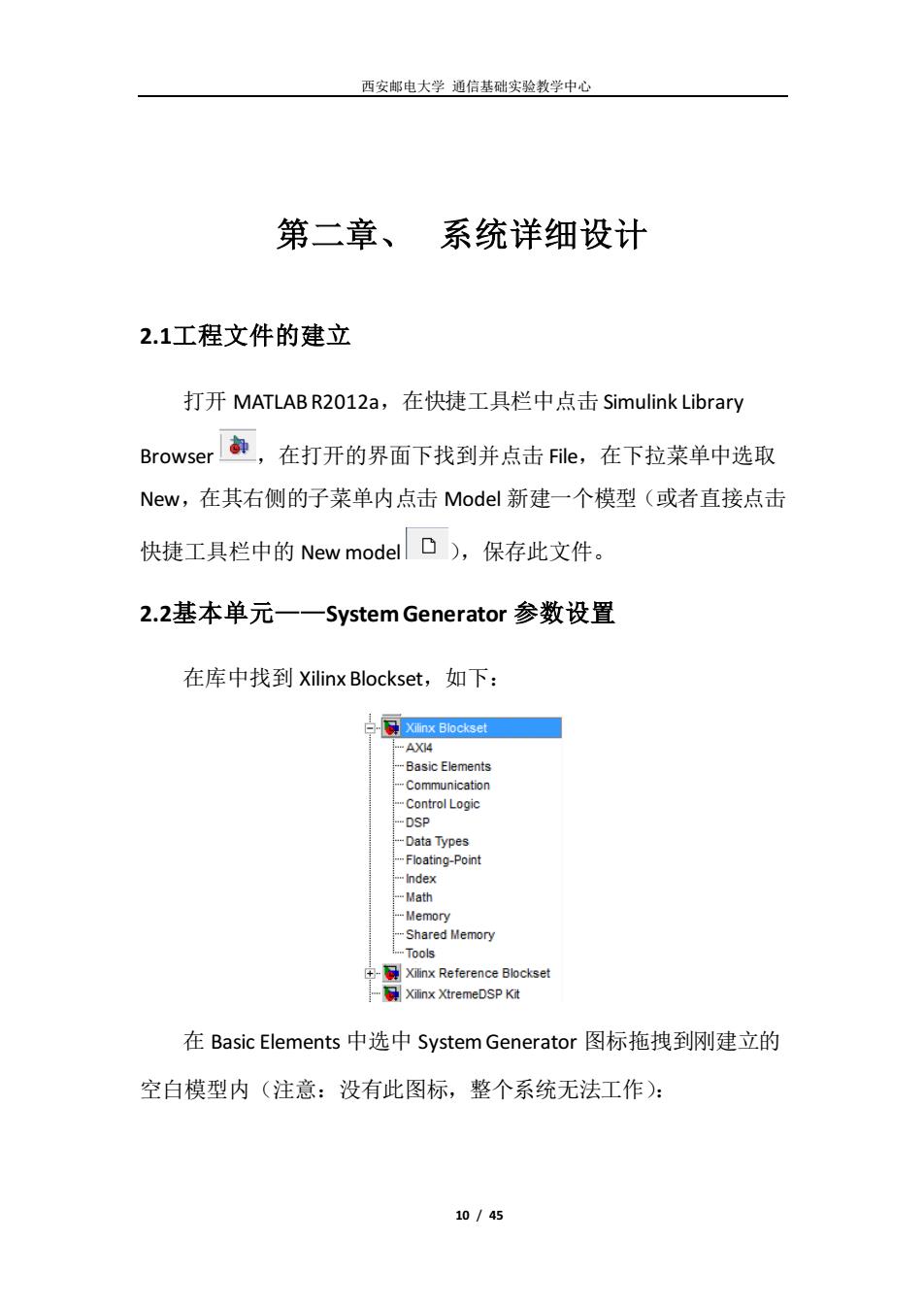

西安邮电大学通信基础实验教学中心 第二章、系统详细设计 2.1工程文件的建立 打开MATLAB R2012a,在快捷工具栏中点击Simulink Library Browser 在打开的界面下找到并点击File,在下拉菜单中选取 New,在其右侧的子菜单内点击Model新建一个模型(或者直接点击 快捷工具栏中的New model),保存此文件。 2.2基本单元一一System Generator参数设置 在库中找到Xilinx Blockset,如下: 白-Xilinx Blockset -AX04 -Basic Elements -Communication -Control Logic DSP -Data Types Floating-Point -Index -Math -Memory Shared Memory LTools Xilinx Reference Blockset Xilinx XtremeDSP Kit 在Basic Elements中选中System Generator图标拖拽到刚建立的 空白模型内(注意:没有此图标,整个系统无法工作): 10/45

西安邮电大学 通信基础实验教学中心 10 / 45 第二章、 系统详细设计 2.1工程文件的建立 打开 MATLAB R2012a,在快捷工具栏中点击 Simulink Library Browser ,在打开的界面下找到并点击 File,在下拉菜单中选取 New,在其右侧的子菜单内点击 Model 新建一个模型(或者直接点击 快捷工具栏中的 New model ),保存此文件。 2.2基本单元——System Generator 参数设置 在库中找到 Xilinx Blockset,如下: 在 Basic Elements 中选中 System Generator 图标拖拽到刚建立的 空白模型内(注意:没有此图标,整个系统无法工作):