《DL语言硬件设计》实验指导书 Librarystm Files Mem hmux_tp.v h] #vsim work.mu民_p #Loading work.mux_tp Loading work.user_mux "Warning:[vsim-3009)[TSCALE]-Module 'user_mux'does not have a 'timescale directive in effect,but previous modules do. Regior:/mux_tp/m1 VSIM 17>run-all 0 a=0b-0 sel-0 out=0 5 a-0b-0 sel-1 out-0 10a-1b-0scl-00-1 15s=1b=0sel-1c=0 20a=0b=1$el=00uM=0 25a-0b=18el-1R=1 30 a-1 b-1 sel-0 out=1 35a-1b-1s8l-1o-1 VSIM 18> Project new sin Now:35 ns Delta:1 sim:/nux_tp wave default Eile Edit yiew Insert Format Tools Findow 含日骨端 品电岛州 男通髓期论 D◆test_MUX4xi/d 1010 1010 田-◇test MUX4x1s 11 Q0可 /test_MUX4x1/out IStT 13)、展开多级左边信号,并放大波形显示,如图所示 waow defals 多日马缩盖鱼回外1网园引世1经潜1正分15道卡可形⑧8®并出引国出送女落世 100 t010 14)、检查输出结果与所设计功能模块所预想的结果是否一致, 如果不一致则更改设计模块中的对应语句。 第11页共49页

《HDL 语言硬件设计》实验指导书 第 11 页 共 49 页 13)、展开多级左边信号,并放大波形显示,如图所示 14)、检查输出结果与所设计功能模块所预想的结果是否一致, 如果不一致则更改设计模块中的对应语句

《DL语言硬件设计》实验指导书 五、试验报告 (1)依照上述步骤写出4选1多路选择器的模块代码,并对其进 行仿真得出仿真结果,并分析仿真结果是否正确,与模块设计功 能是否一致? (2)如给出如下4位全加器的门级结构设计代码,请进行仿真测 试,并自己编写3位全加器模块代码和仿真模块代码,并进行仿 真,分析仿真结果是否正确,与模块设计功能是否一致? 第12页共49页

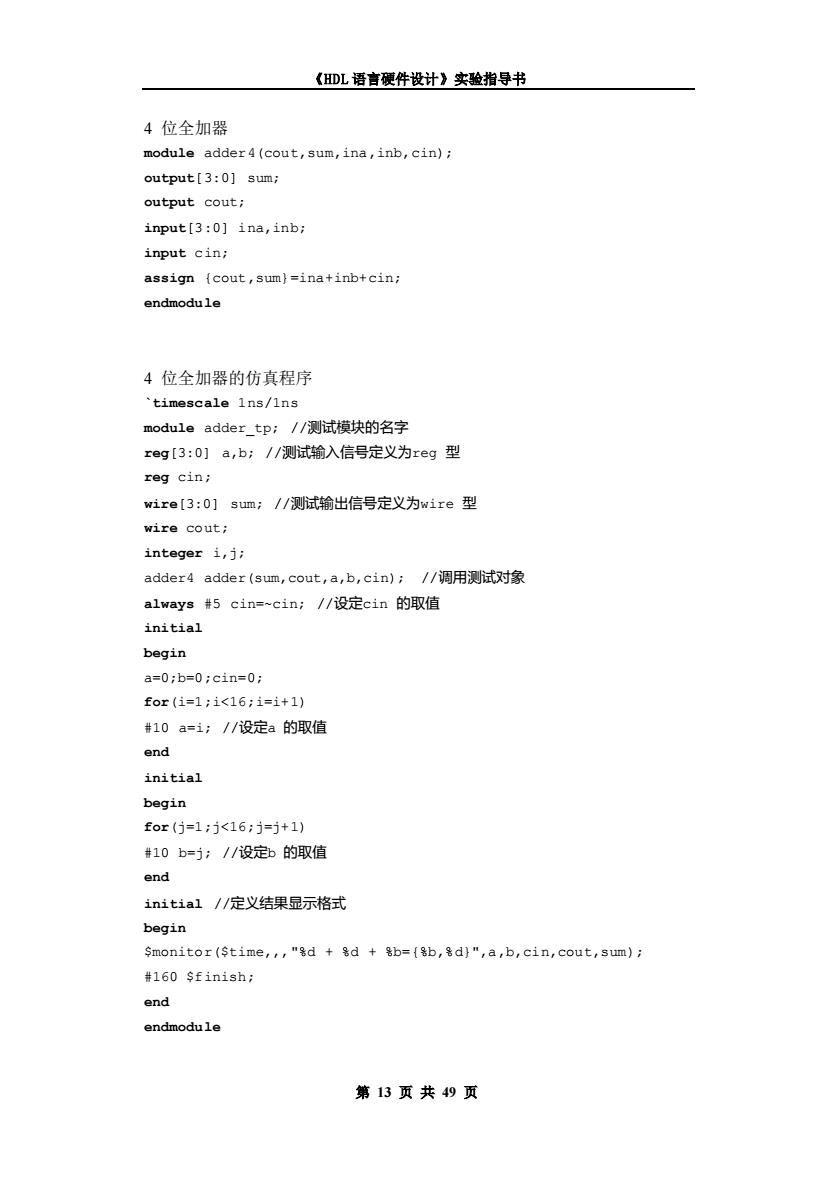

《HDL 语言硬件设计》实验指导书 第 12 页 共 49 页 五、试验报告 (1)依照上述步骤写出 4 选 1 多路选择器的模块代码,并对其进 行仿真得出仿真结果,并分析仿真结果是否正确,与模块设计功 能是否一致? (2)如给出如下 4 位全加器的门级结构设计代码,请进行仿真测 试,并自己编写 3 位全加器模块代码和仿真模块代码,并进行仿 真,分析仿真结果是否正确,与模块设计功能是否一致?

《DL语言硬件设计》实验指导书 4位全加器 module adder4(cout,sum,ina,inb,cin); output[3:0]sum; output cout; input[3:0]ina,inb; input cin; assign (cout,sum}=ina+inb+cin; endmodule 4位全加器的仿真程序 timescale 1ns/1ns module adder tp;/测试模块的名字 reg[3:0]a,b;/测试输入信号定义为reg型 reg cin; wire[3:0]sum:/测试输出信号定义为wire型 wire cout; integer i,j; adder4 adder(sum,cout,a,b,cin);//调用测试对象 always#5cin=~cin;/设定cin的取值 initial begin a=0:b=0;cin=0: for(i=1;1<16;i=i+1) #10a=i;//设定a的取值 end initial begin for(j=1;j<16;j=j+1) #10b=j;/设定b的取值 end initial/定义结果显示格式 begin $monitor($time,"号d+号d+b={号b,gd}",a,b,cin,cout,sum); #160 sfinish; end endmodule 第13页共49页

《HDL 语言硬件设计》实验指导书 第 13 页 共 49 页 4 位全加器 module adder4(cout,sum,ina,inb,cin); output[3:0] sum; output cout; input[3:0] ina,inb; input cin; assign {cout,sum}=ina+inb+cin; endmodule 4 位全加器的仿真程序 `timescale 1ns/1ns module adder_tp; //测试模块的名字 reg[3:0] a,b; //测试输入信号定义为reg 型 reg cin; wire[3:0] sum; //测试输出信号定义为wire 型 wire cout; integer i,j; adder4 adder(sum,cout,a,b,cin); //调用测试对象 always #5 cin=~cin; //设定cin 的取值 initial begin a=0;b=0;cin=0; for(i=1;i<16;i=i+1) #10 a=i; //设定a 的取值 end initial begin for(j=1;j<16;j=j+1) #10 b=j; //设定b 的取值 end initial //定义结果显示格式 begin $monitor($time,"%d + %d + %b={%b,%d}",a,b,cin,cout,sum); #160 $finish; end endmodule

《DL语言硬件设计》实验指导书 第14页共49页

《HDL 语言硬件设计》实验指导书 第 14 页 共 49 页

《DL语言硬件设计》实验指导书 (3)写出实验心得,和对课程和实验的一些建议,不少于100字。 第15页共49页

《HDL 语言硬件设计》实验指导书 第 15 页 共 49 页 (3)写出实验心得,和对课程和实验的一些建议,不少于 100 字