《数字系统与FPGA设计》实验指导书 3、列出用LPM宏定制RAM和ROM的仿真结果。 五、思考题 1、Quartus IⅡ5.1仿真平台由哪三部分组成,各自作用是什么? 第6页共31页

《数字系统与 FPGA 设计》实验指导书 第 6 页 共 31 页 3、列出用 LPM 宏定制 RAM 和 ROM 的仿真结果。 五、思考题 1、QuartusⅡ5.1 仿真平台由哪三部分组成,各自作用是什么?

《数字系统与FPGA设计》实验指导书 2、什么是P,如何进行分类? 3、如何进行宏模块定制,在使用上有何原则? 第7页共31页

《数字系统与 FPGA 设计》实验指导书 第 7 页 共 31 页 2、什么是 IP,如何进行分类? 3、如何进行宏模块定制,在使用上有何原则?

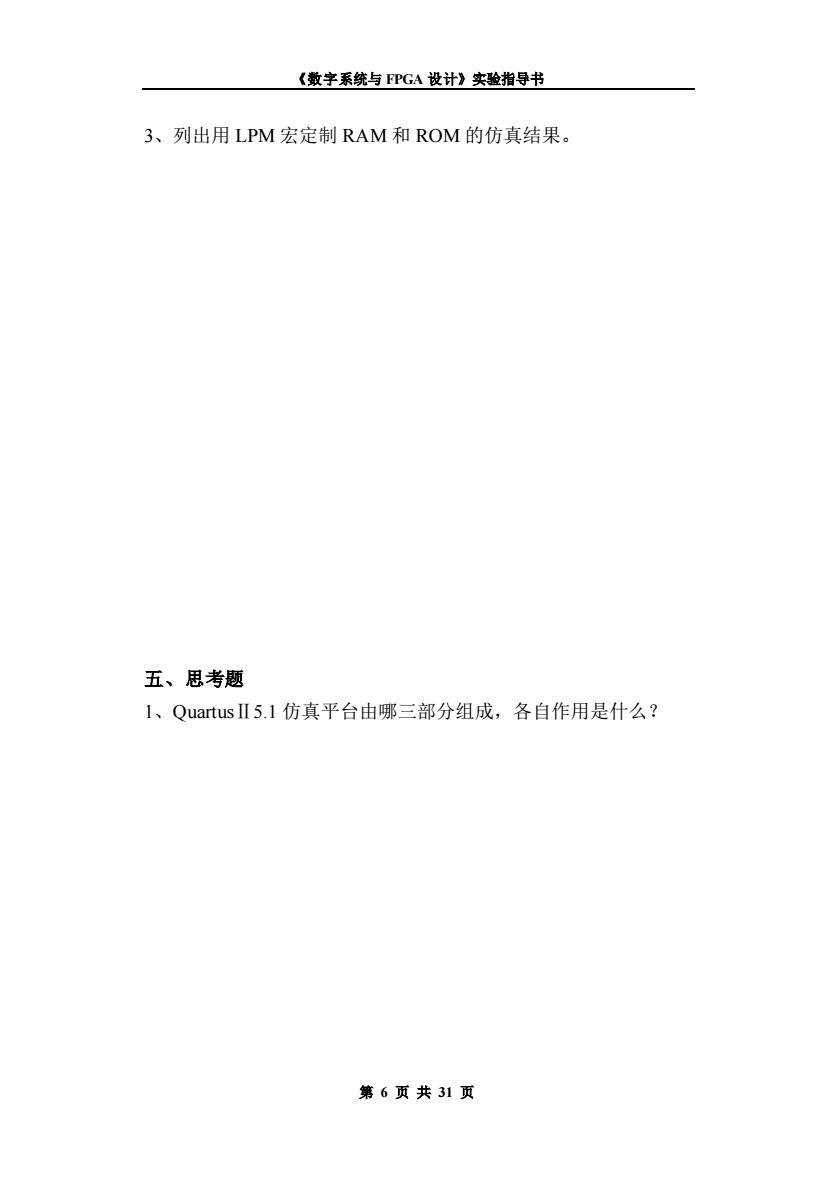

《数字系统与FPGA设计》实验指导书 实验三8bt无符号数串行硬件乘法器模块设计 和功能仿真(2学时) 一、实验要求 用一个8bit加法器串行相加实现,模块如下图。完成模块设 计和功能仿真。 my mult4 reset done clk product[15.0] st mull8.0] muld 8.0] inst 输入输出说明: Reset:复位 C1k:时钟 St:启动信号 Done:运算结束信号 Mul:乘数 Muld:被乘数 第8页共31页

《数字系统与 FPGA 设计》实验指导书 第 8 页 共 31 页 实验三 8bit 无符号数串行硬件乘法器模块设计 和功能仿真(2 学时) 一、实验要求 用一个 8bit 加法器串行相加实现,模块如下图。 完成模块设 计和功能仿真。 输入输出说明: Reset:复位 Clk:时钟 St:启动信号 Done:运算结束信号 Mul:乘数 Muld:被乘数

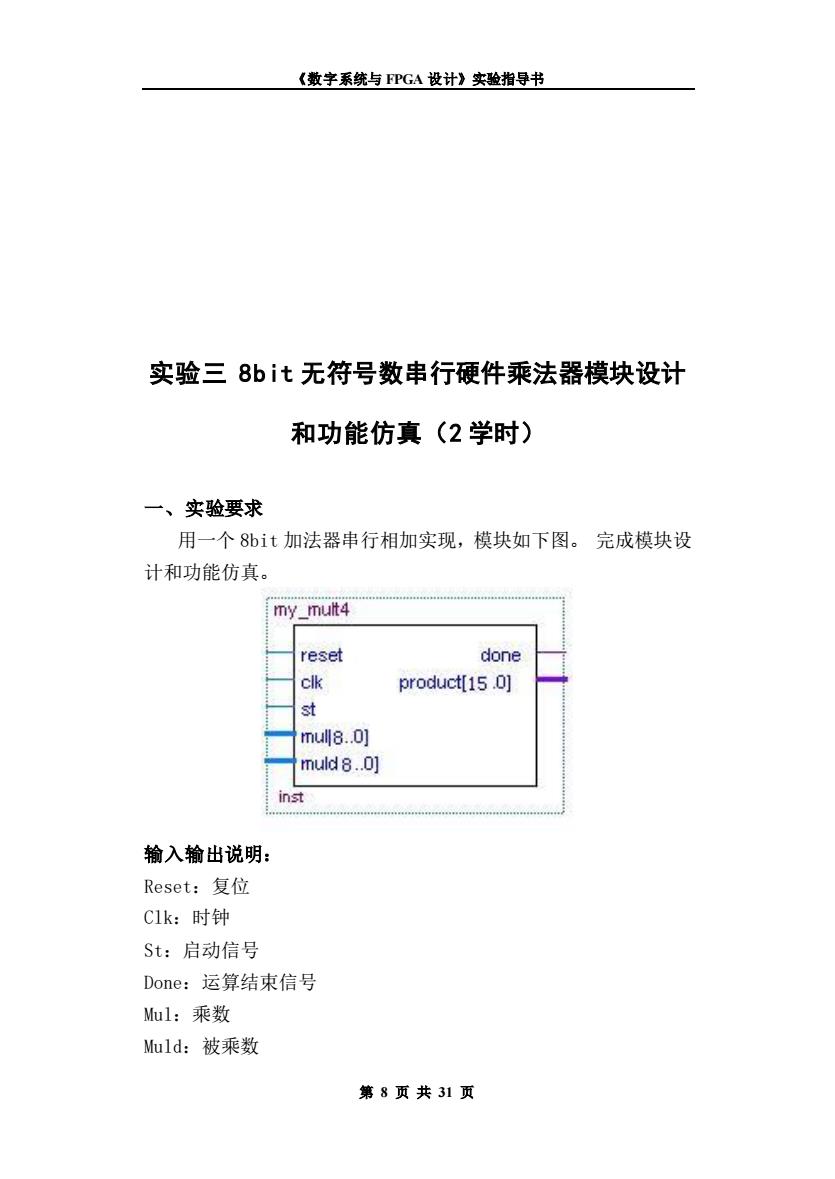

《数字系统与FPGA设计》实验指导书 Product:运算结果 二、实验设备 PC机 一台 Quartus IⅡ开发软件 三、实验原理: 1.模块体系结构 模块主要由三大部分构成,控制单元负责控制逻辑、移位累加 器和加法计数器实现具体数据处理和数据路径。 控 移位累加器 单元 加法计数器 2.乘法原理算法模型如下图: 第9页共31页

《数字系统与 FPGA 设计》实验指导书 第 9 页 共 31 页 Product:运算结果 二、实验设备 PC 机 一台 QuartusⅡ开发软件 三、实验原理: 1.模块体系结构 模块主要由三大部分构成,控制单元负责控制逻辑、移位累加 器和加法计数器实现具体数据处理和数据路径。 2.乘法原理算法模型如下图: 控 制 单 元 移位累加器 加法计数器

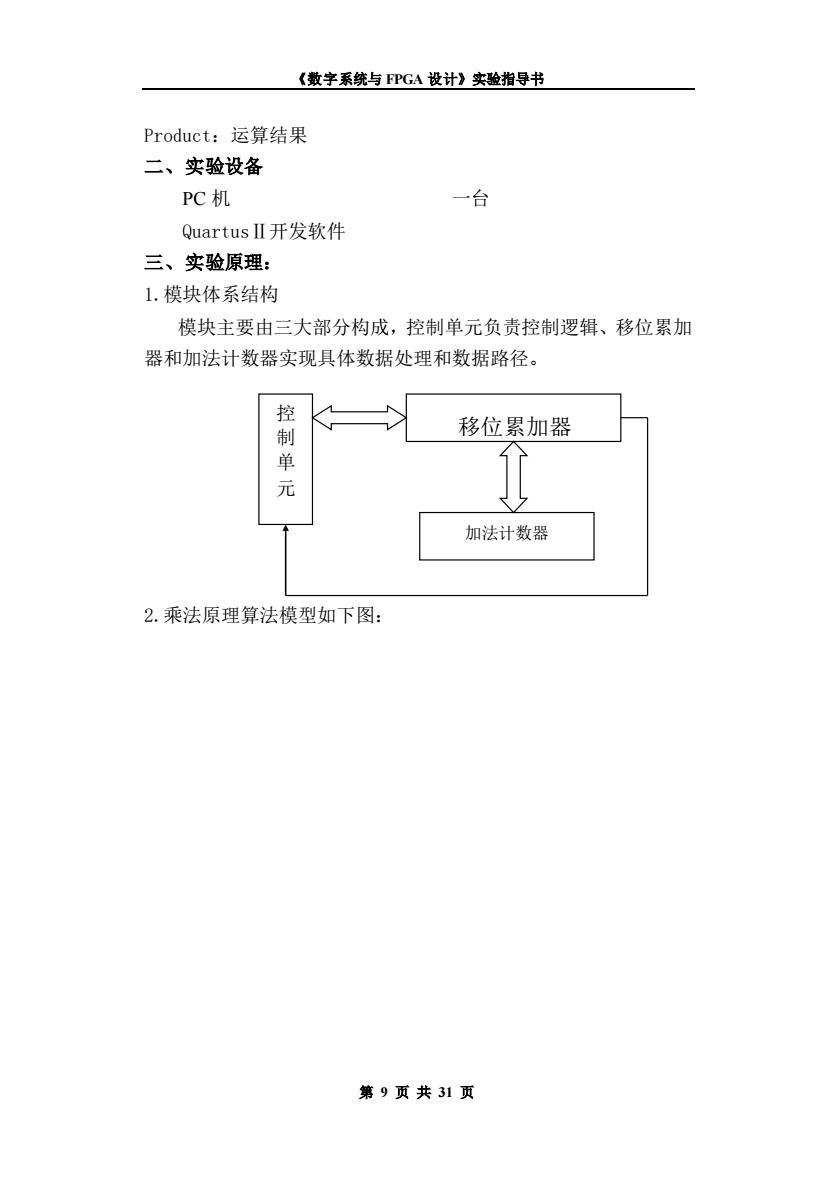

after shift 0011011101—M (add multiplicand since M=1) 1101 after addition 100111101 after shift 0100111i10—M (skip addition since M=0) after shift 0010011111←-M (add multiplicand since M=1) 1101 after addition 100011110 after shift (final answer) 0100011111 (143) dividing line between product and multiplier 四、实验步骤 l.使用quartus?2设计软件建立工程文件。由file>New> block/.进入,由模块实现选择进入。 2.使用verilog语言设计控制单元,用模块编辑器调用宏器件设 计乘法器的移位累加器和加法计数器。(参见课件第二讲模块 编辑器内容) 3.根据设计要求建立仿真激励文件。(参见课件第二讲Quartus2 仿真工具内容) 4.编译定制乘法器模块,并在simulator tool中点击【Start】, 运行仿真器进行功能仿真。 五、实验电路描述与实验结果 1.模块算法流程图及说明。 第10页共31页

《数字系统与 FPGA 设计》实验指导书 第 10 页 共 31 页 四、实验步骤 1. 使用 quartus2 设计软件建立工程文件。由 file> New> block/.进入,由模块实现选择进入。 2. 使用 verilog 语言设计控制单元,用模块编辑器调用宏器件设 计乘法器的移位累加器和加法计数器。(参见课件第二讲模块 编辑器内容) 3. 根据设计要求建立仿真激励文件。(参见课件第二讲 Quartus2 仿真工具内容) 4. 编译定制乘法器模块,并在 simulator tool 中点击【Start】, 运行仿真器进行功能仿真。 五、实验电路描述与实验结果 1.模块算法流程图及说明