一个完整的Sysgen设计 Simulink SysGen Data Path and Sinks分析 helper blocks用FPGA实现的设计 结果 sysgenFIBONACC_logic* Fle Edit View Simulation Format Tools Help 2+■ Nomal 用Play按 钮开始 1.9)12r0 ib(n Out 仿真,后 Signal From Workspace 边框中 zerc1.9)12 n Out 的数字 Signal From lsValid 9000 Worksoaoe1 Fibonacci 是仿真 时间长 度,单位 System Resource 秒 Generator Ready 100% FixedStepDiscrete Simulink Sources Gateway blocks用来做Simulink和 测试激励 SysGen之间的接口 Intro to System Generator -02-17 2006 Xilinx.Inc.All Rights Reserved XILINX

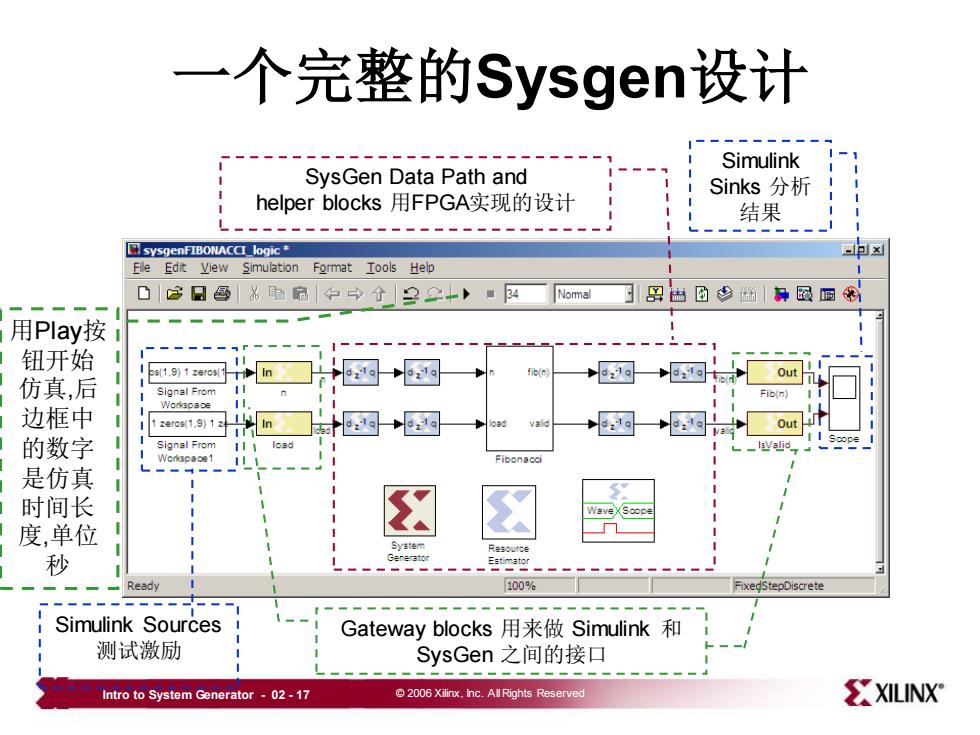

Intro to System Generator - 02 - 17 © 2006 Xilinx, Inc. All Rights Reserved 一个完整的Sysgen设计 Simulink Sources 测试激励 Simulink Sinks 分析 结果 Gateway blocks 用来做 Simulink 和 SysGen 之间的接口 SysGen Data Path and helper blocks 用FPGA实现的设计 用Play按 钮开始 仿真,后 边框中 的数字 是仿真 时间长 度,单位 秒

创建子系统 .大的设计可以分多个层次 用鼠标拖出一个框把要 n 放在子系统的部分选中 ◆aty0时 按右键选Create Subsystem atear Outt Sine WYavet Gatewy int AddSub Or press Ctrl+G .用View菜单下的modelbrowser 浏览系统的层次关系, m 0.tl 或双击进入子系统 Gatarayr Out .子系统决定了HDL代码 0t2 Gateay Out1 和网表的层次关系 Subsystem Intro to System Generator -02-18 2006 Xilinx.Inc.All Rights Reserved XILINX

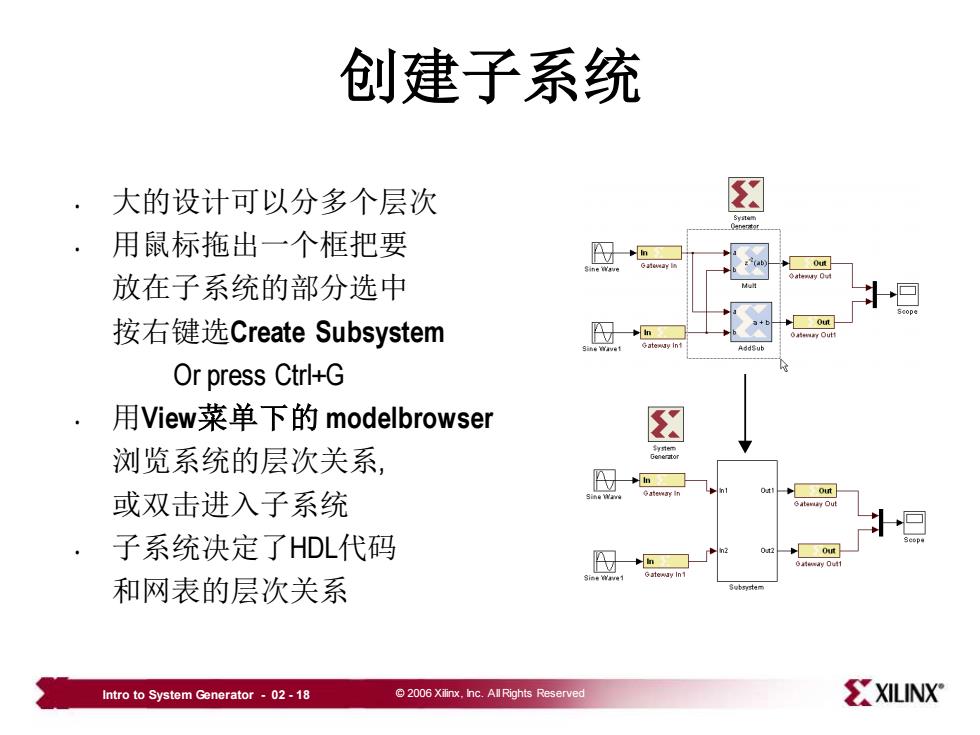

Intro to System Generator - 02 - 18 © 2006 Xilinx, Inc. All Rights Reserved 创建子系统 • 大的设计可以分多个层次 • 用鼠标拖出一个框把要 放在子系统的部分选中 按右键选Create Subsystem Or press Ctrl+G • 用View菜单下的 modelbrowser 浏览系统的层次关系, 或双击进入子系统 • 子系统决定了HDL代码 和网表的层次关系

Model的Callback函数 0005 导当回梦色國圆多 .在空白处点右键 FIR Low-Pass Filter 选择Model Properties 其中的Callbacks拦非常有用 Can't Undo Can't Redo Paste Model Properties Paste Duplicate Inport Main Calibacks History Description Select All Remove Highlighting Model callbacks Model pre-load function: -PreLoadFcn" fs=100e6 Highlight . -PostLoadFcn beta =10 Back InitFcn StartFcn Forward Stoofcn Go To Parent Workspace 回☒ Link Options Eile Edit View Graphics Debug Desktop Window Help Update Diagram oefficient oad Engine 省国想 昌 海 园 Stack: Base Configuration Parameters. Tool Model Properties Name Value Min Max Fixed-Point Settings. 田fs 250000000 2500. 2500. m 田simout <159x1 double> -0.00.0.1624 Tool1 Signal Scope Manager. 目sysgenguivars <1x1 struct> Screen Color 田tout <159x1 double> 0 0 Help Apply Library Link Display ☒xISgRoot C:\Tools\dsptools\9.2.00.967\sysgen\bir Format 田xl_pb_trace Help 2006 Xilinx,Inc.All Rights Reserved XILINX

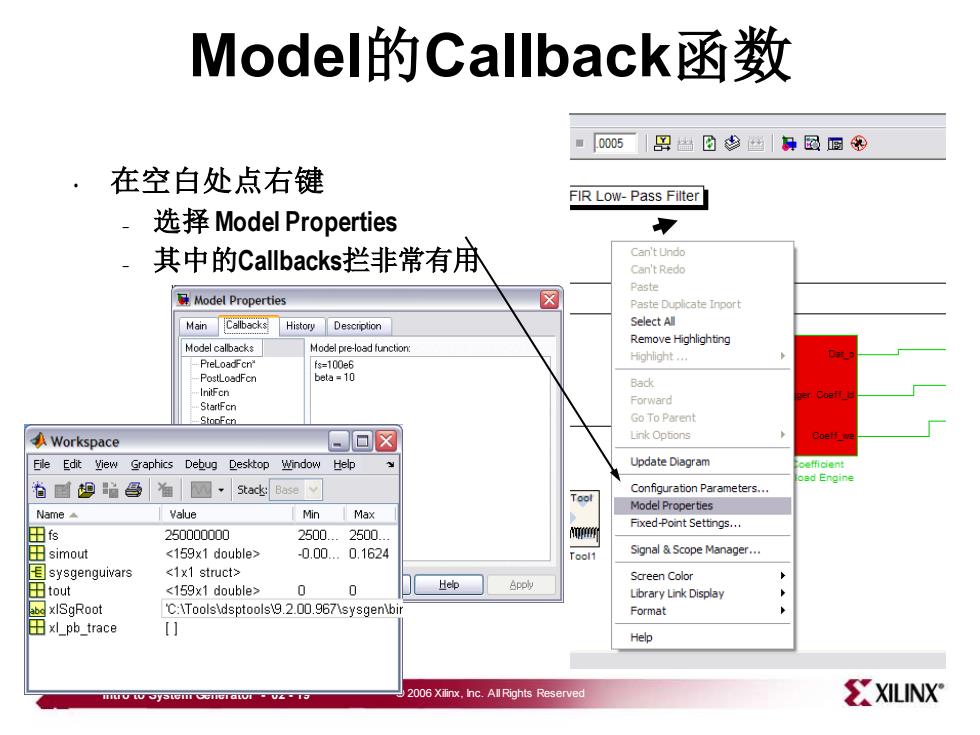

Intro to System Generator - 02 - 19 © 2006 Xilinx, Inc. All Rights Reserved Model的Callback函数 • 在空白处点右键 – 选择 Model Properties – 其中的Callbacks拦非常有用

提纲 .System Generator概述 .基础入门 ·采样周期及多速率设计 ·数据类型及类型转换 ·控制逻辑及DL协同仿真 .硬件协同仿真 ·系统集成 Intro to System Generator -02-20 2006 Xilinx.Inc.All Rights Reserved XILINX

Intro to System Generator - 02 - 20 © 2006 Xilinx, Inc. All Rights Reserved 提纲 • System Generator概述 • 基础入门 • 采样周期及多速率设计 • 数据类型及类型转换 • 控制逻辑及HDL协同仿真 • 硬件协同仿真 • 系统集成

采样周期Sample Period 在Simulink中没有时钟,只有采样周期Sample Period,Sysgen中所 有时序由采样周期定义 Sysgen中的信号都必须是“sampled'”,变化发生在等间隔的离散 时间点,即采样周期Sample Period 每个block的“sample period,”决定block的功能多长时间计算一 次并输出结果 Block的sample period直接决定在FPGA硬件中时钟驱动方式 有些Block的Sample period必须设置,如: . Gateway In 没有输入的Block,如Counter 其它blocks的Sample period可以从输入信号继承 设置sample periodsl时要注意奈奎斯特定律(Fs≥2fmax) Intro to System Generator -02-21 2006 Xilinx.Inc.All Rights Reserved XILINX

Intro to System Generator - 02 - 21 © 2006 Xilinx, Inc. All Rights Reserved 采样周期Sample Period • 在Simulink 中没有时钟, 只有采样周期Sample Period, Sysgen中所 有时序由采样周期定义 • Sysgen中的信号都必须是 “sampled”; 变化发生在等间隔的离散 时间点, 即采样周期Sample Period • 每个block 的 “sample period,” 决定block的功能多长时间计算一 次并输出结果 • Block的sample period直接决定在FPGA硬件中时钟驱动方式 • 有些Block的Sample period必须设置,如: • Gateway In • 没有输入的Block, 如Counter • 其它blocks的Sample period可以从输入信号继承 • 设置sample periods时要注意奈奎斯特定律 (Fs 2fmax)