System Generator Token Simulink System Period在逻辑上与FPGA系统时钟的周期相对应 Simulink System Period(单位为 System Generator:counter_enabled Xilinx System Generator 秒)必须在SysGen token中设 Compilation 置正确.对于single-rate单速率 ☒HDL Netlist Settings. 系统,要和设计中的sample Part: System Virtex4 xc4vfx12-10ff668 periods一致.在multi-rate多 Target Directory: 速率设计中要和设计中所有 /netlist Browse. sample periods的最大公约数 Synthesis Tool: Hardware Description Language XST VHDL 一致 FPGA Clock Period (ns) Clock Pin Location: 10 AE14 dbl fpt ☐Create Tastbench Import as Configurable Subsystem input1 (ab Provide clock enable clear pin dbl fpt input2 Mult fpt dbl overnide with Doubles According to Block Settings dbl fpt Out Add1 Simulink System Period (sec) input3 (ab fpt Block Icon Display Default Mult1 input4 Generate OK Apply Cancel Help Sample Period=1 Intro to System Generator -02-12 2006 Xilinx,Inc.All Rights Reserved XILINX

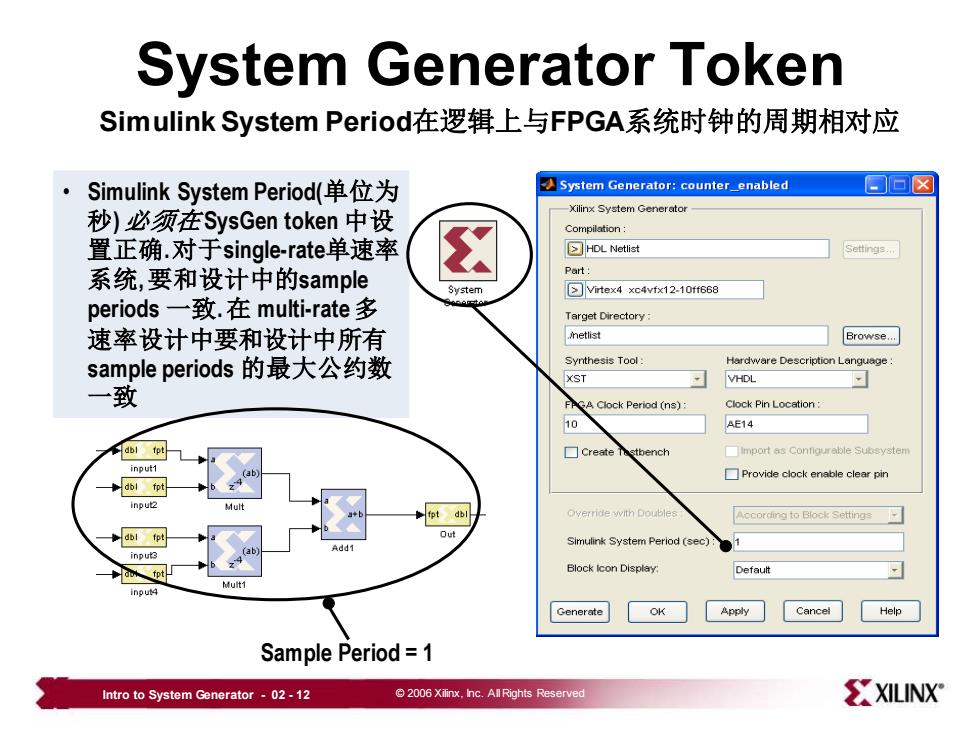

Intro to System Generator - 02 - 12 © 2006 Xilinx, Inc. All Rights Reserved • Simulink System Period(单位为 秒) 必须在SysGen token 中设 置正确. 对于single-rate单速率 系统, 要和设计中的sample periods 一致. 在 multi-rate 多 速率设计中要和设计中所有 sample periods 的最大公约数 一致 System Generator Token Sample Period = 1 Simulink System Period在逻辑上与FPGA系统时钟的周期相对应

System Generator Token 设计完成,仿真正确后,双击 A CAM Systam with Packet Framing and FEC for Telemetry Channels 打开System Generator token System Generator:counter_enabled ]回☒ xilinx System Generator Complotion: 习HDL Netlist Settings_ Part Virtex4 xc4vfx12-1011668 Target Directory /etlist Browse. 设置好FPGA实现参数 Syrthesis格Tcal Hardware Description Language XST VHDL FPGA Clock Period (ns) Clock Pin Location 10 AE14 点击Generate按钮即可按FPGA的 ☐Create Testbench Import as Configurable Subsyitem Provide clock enable clear pin 编译目标调用相应的FPGA工具进 Override vyitn Doubles 人ccordng to可ock Settings 行FPGA设计的编译实现,生成HDL Smulink System Period (sec): 代码,NGC网表等文件 Block Icon Displey. Default Generate OK Apply Cancel Help Intro to System Generator -02-13 2006 Xilinx.Inc.All Rights Reserved XILINX

Intro to System Generator - 02 - 13 © 2006 Xilinx, Inc. All Rights Reserved System Generator Token • 设置好FPGA实现参数 • 点击Generate按钮即可按FPGA的 编译目标调用相应的FPGA工具进 行FPGA设计的编译实现, 生成HDL 代码, NGC网表等文件 设计完成,仿真正确后,双击 打开System Generator token

Gateway In In Gateway In 把Simulink的浮点数转换成定点数,送给SysgenI的FPGA设计,功能 相当于信号系统中的ADC .定义J顶层设计中的输入端口,对应HDL设计中的input ports Gateway Out Out Gateway Out 把Sysgent的FPGA设计的定点数转换成浮点数送给Simulink,功能 相当于信号系统中的DAC 定义顶层设计中的输出端口,对应HDL设计中的output ports Intro to System Generator -02-14 2006 Xilinx.Inc.All Rights Reserved XILINX

Intro to System Generator - 02 - 14 © 2006 Xilinx, Inc. All Rights Reserved Gateway In • 把Simulink的浮点数转换成定点数,送给Sysgen的FPGA设计,功能 相当于信号系统中的ADC • 定义顶层设计中的输入端口,对应HDL设计中的input ports Gateway Out • 把Sysgen的FPGA设计的定点数转换成浮点数送给Simulink,功能 相当于信号系统中的DAC • 定义顶层设计中的输出端口,对应HDL设计中的output ports

开始System Generator设计 和一般Simulink设计类似:打开Simulink Liberary Browser->创建新 的Model->从Simulink Liberary Browser中选择适当的Block拖入Model ->设置Block属性>Block互连>系统仿真>编译实现 Simulink Diagram 01:1 na+,4t门非 t甘,011封 军。海其速 Simulink Library Browser MATLAB 注意:Matlab的当前路径必须指向你的工作路径 Intro to System Generator -02-15 2006 Xilinx.Inc.All Rights Reserved XILINX

Intro to System Generator - 02 - 15 © 2006 Xilinx, Inc. All Rights Reserved 开始System Generator设计 MATLAB Simulink Library Browser Simulink Diagram • 和一般Simulink设计类似: 打开Simulink Liberary Browser -> 创建新 的Model -> 从Simulink Liberary Browser中选择适当的Block拖入Model -> 设置Block属性 -> Block互连 -> 系统仿真 -> 编译实现 注意: Matlab的当前路径必须指向你的工作路径

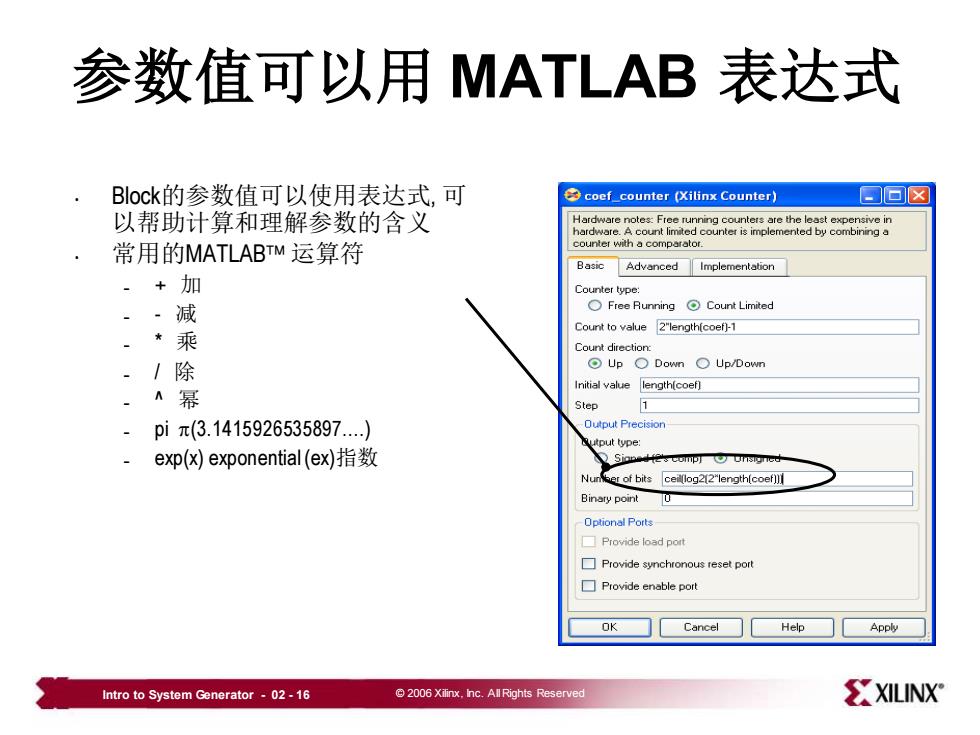

参数值可以用MATLAB表达式 Block的参数值可以使用表达式,可 coef_counter (Xilinx Counter) ▣☒ 以帮助计算和理解参数的含义 Hardware notes:Free running counters are the least expensive in hardware.A count limited counter is implemented by combining a 常用的MATLABTM运算符 counter with a comparator. Basic Advanced Implementation 。+加 Counter type: 减 ○Free Running Count Limited Count to value 2"length(coef]-1 乘 Count direction 。1除 Up Down○Up/Dowm Initial value length(coef] 幂 Step 1 piπ(3.1415926535897.) Output Precision uput type: exp(x)exponential(ex指数 SiapeHe's cump]Unisignce Nunher of bits ceil(log2(2"length(coef]] Binary point Optional Ports ☐Provide load port Provide synchronous reset port ☐Provide enable port OK Cancel Help Apply Intro to System Generator -02-16 2006 Xilinx.Inc.All Rights Reserved XILINX

Intro to System Generator - 02 - 16 © 2006 Xilinx, Inc. All Rights Reserved 参数值可以用 MATLAB 表达式 • Block的参数值可以使用表达式, 可 以帮助计算和理解参数的含义 • 常用的MATLAB 运算符 – + 加 – - 减 – * 乘 – / 除 – ^ 幂 – pi (3.1415926535897.) – exp(x) exponential (ex)指数