第八讲可综合设计 西安邮电学院通信工程系 第八讲可综合设计与时序仿真 内容: 冬逻辑综合概念 ÷逻辑综合流程和工具 Verilog可综合语句 冬RTL级可综合设计 时序仿真

第八讲 可综合设计 西安邮电学院通信工程系 第 八讲 可综合设计与时序仿真 内容: ❖ 逻辑综合概念 ❖ 逻辑综合流程和工具 ❖ Verilog可综合语句 ❖ RTL级可综合设计 ❖ 时序仿真

第八讲可综合设计 西安邮电学院通信工程系 Verilog HDL的设计流程 技术指标: 系统描述 用文字表示 用算法表示 系统仿真 用高级行为的erilog模块表示 RTL级设计 RTL/功能级: ↓ 用可综合的Verilog模块表示 功能(前)仿真 ↓ 门级/结构级: 逻辑综合 用实例引用的Verilog模块表示 1 门级仿真 版图布局/物理级: ↓ 用几何形状来表示 布局布线 ↓ 后仿真

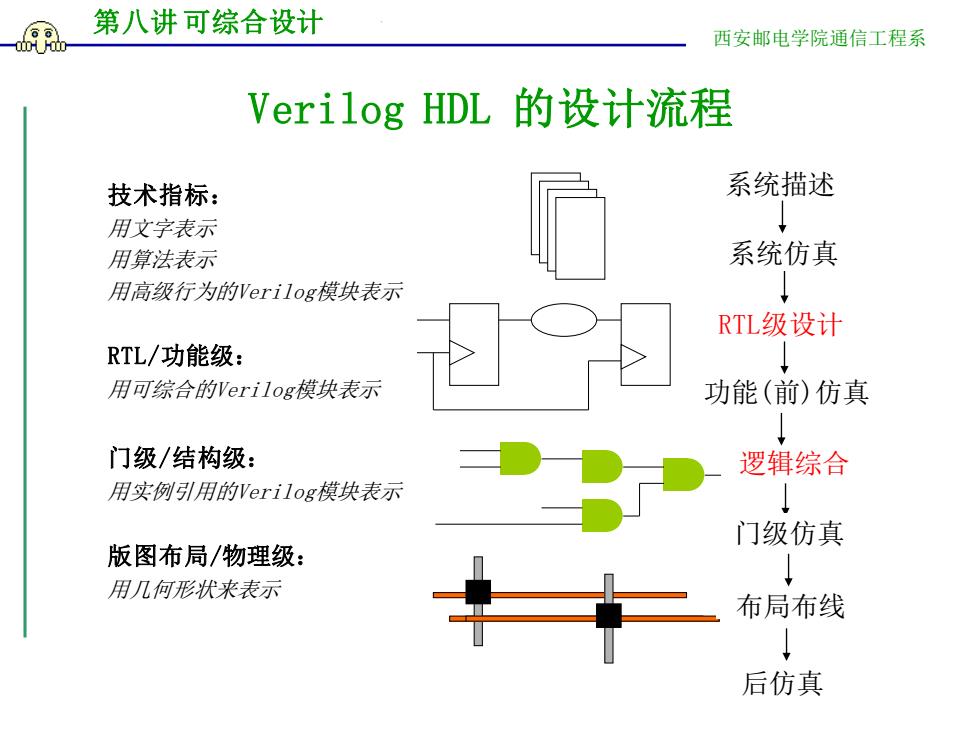

第八讲 可综合设计 西安邮电学院通信工程系 Verilog HDL 的设计流程 技术指标: 用文字表示 用算法表示 用高级行为的Verilog模块表示 RTL/功能级: 用可综合的Verilog模块表示 门级/结构级: 用实例引用的Verilog模块表示 版图布局/物理级: 用几何形状来表示 功能(前)仿真 系统描述 逻辑综合 系统仿真 后仿真 布局布线 门级仿真 RTL级设计

第八讲可综合设计 西安邮电学院通信工程系 逻辑综合概念 逻辑综合:将DL模块的行为描述转换成门级电路,并优化电路结构。 always @(a or b or c or d or sel) begin inferred mux_out case(sel) 2'b00:mux_out a; QU 2b'01:mux_out b; sel 2b'10:mux_out c; 2'b11:mux out d; endcase Translation Optimization

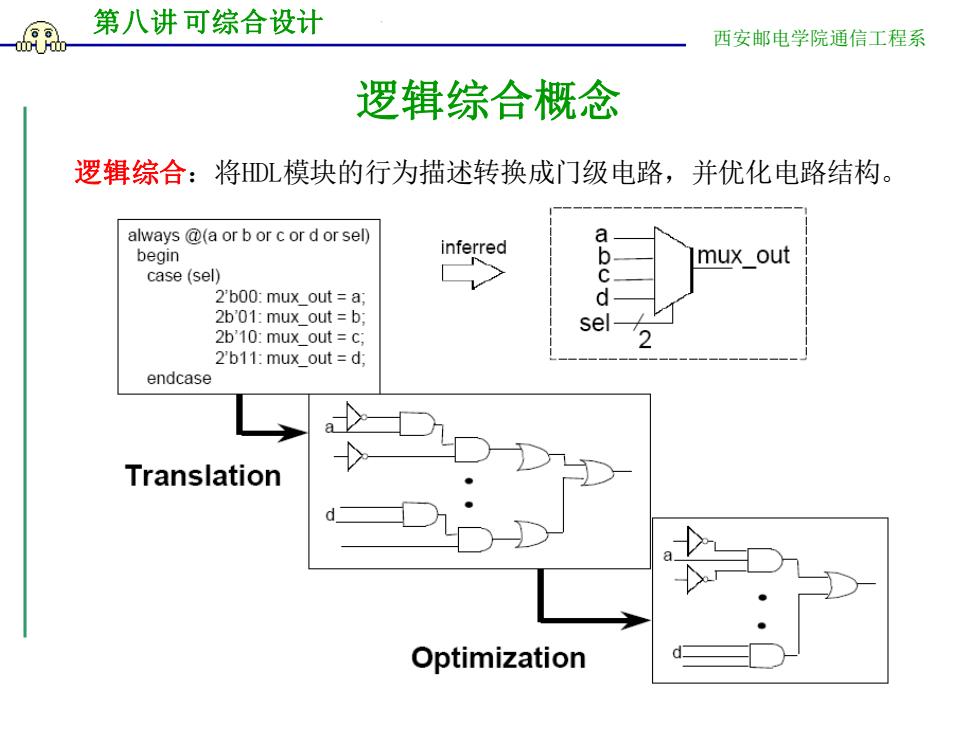

第八讲 可综合设计 西安邮电学院通信工程系 逻辑综合概念 逻辑综合:将HDL模块的行为描述转换成门级电路,并优化电路结构

第八讲可综合设计 西安邮电学院通信工程系 逻辑综合流程和工具 Verilog Technology Model Library 常用的综合工具: Synplify Synthesis Designer compiler Compiler Timing Analysis Netlist Place/Route Text Output Test Simulation Vectors Waveform

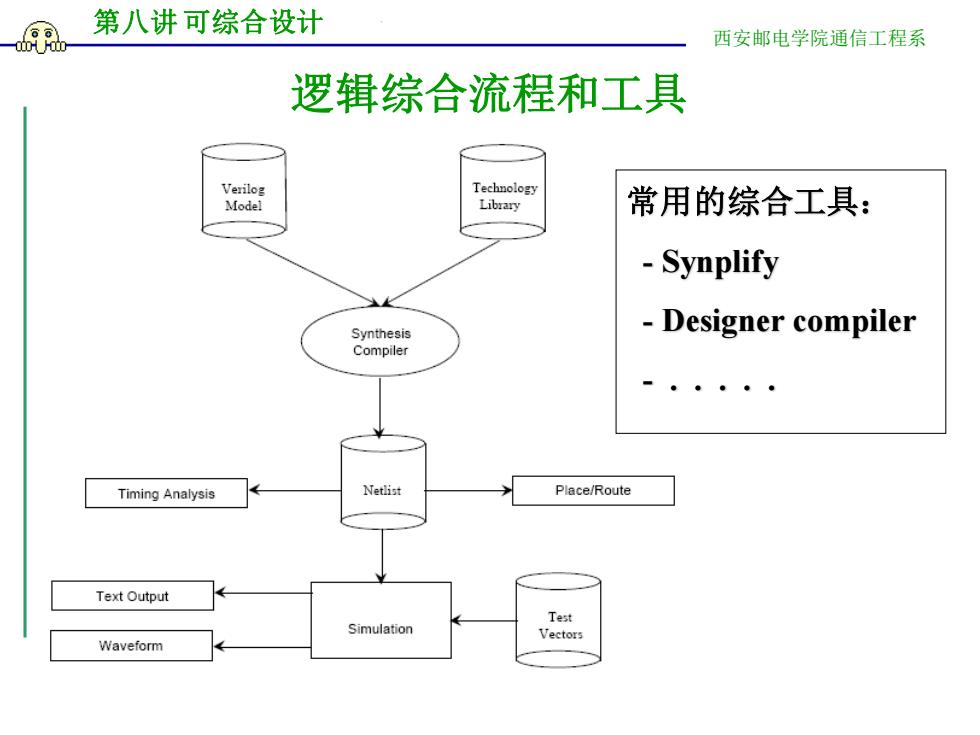

第八讲 可综合设计 西安邮电学院通信工程系 逻辑综合流程和工具 常用的综合工具: - Synplify - Designer compiler - . . . .

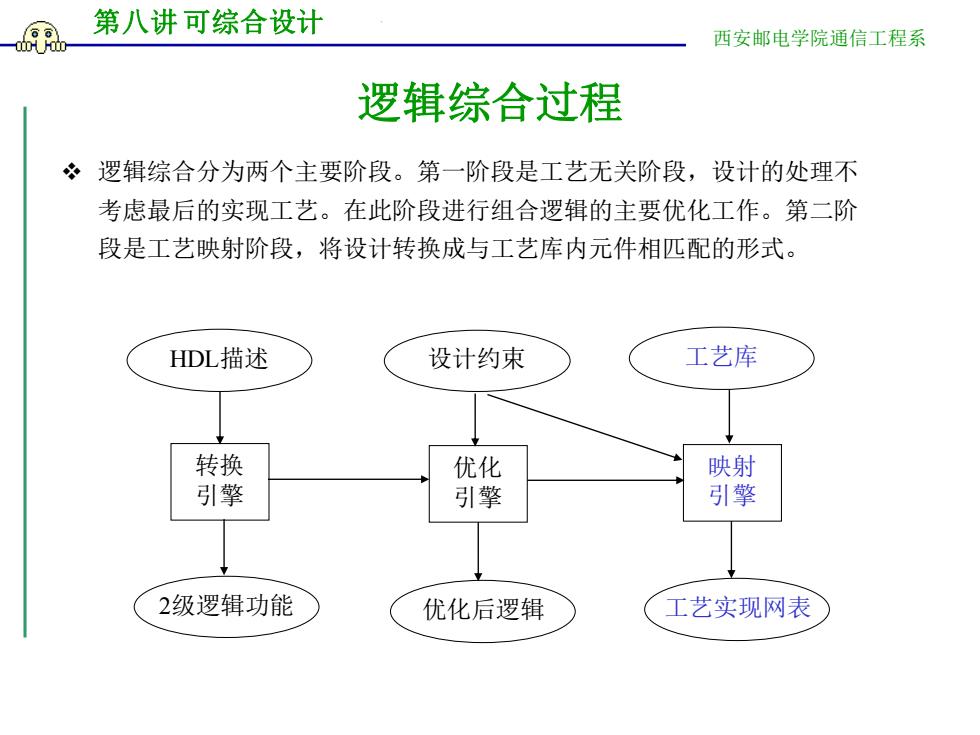

第八讲可综合设计 西安邮电学院通信工程系 逻辑综合过程 冬逻辑综合分为两个主要阶段。第一阶段是工艺无关阶段,设计的处理不 考虑最后的实现工艺。在此阶段进行组合逻辑的主要优化工作。第二阶 段是工艺映射阶段,将设计转换成与工艺库内元件相匹配的形式。 HDL描述 设计约束 工艺库 转换 优化 映射 引擎 引擎 引擎 2级逻辑功能 优化后逻辑 工艺实现网表

第八讲 可综合设计 西安邮电学院通信工程系 逻辑综合过程 ❖ 逻辑综合分为两个主要阶段。第一阶段是工艺无关阶段,设计的处理不 考虑最后的实现工艺。在此阶段进行组合逻辑的主要优化工作。第二阶 段是工艺映射阶段,将设计转换成与工艺库内元件相匹配的形式。 HDL描述 转换 引擎 2级逻辑功能 优化后逻辑 工艺实现网表 工艺库 优化 引擎 映射 引擎 设计约束