第八讲可综合设计 西安邮电学院通信工程系 工艺库与设计约束 工艺库(标准单元库):是由器件制造公司提供的库 单元集合。库单元可以是基本逻辑门或宏单元,用 verilog或其它语言建模,描述库单元的特性包括:单 元的功能、时序、功耗和面积。 冬设计约束:通常包含如下内容。 ■时序:电路必须满足的时序要求。 面积 面积:最终电路实现的面积或资 源占用量。 ·功耗:电路功耗不得超过的上界。 ·工作环境:管脚分布与输入输出 延时 延时、驱动强度和负载,环境温 度,电压等。 如图示:面积与速度的折中

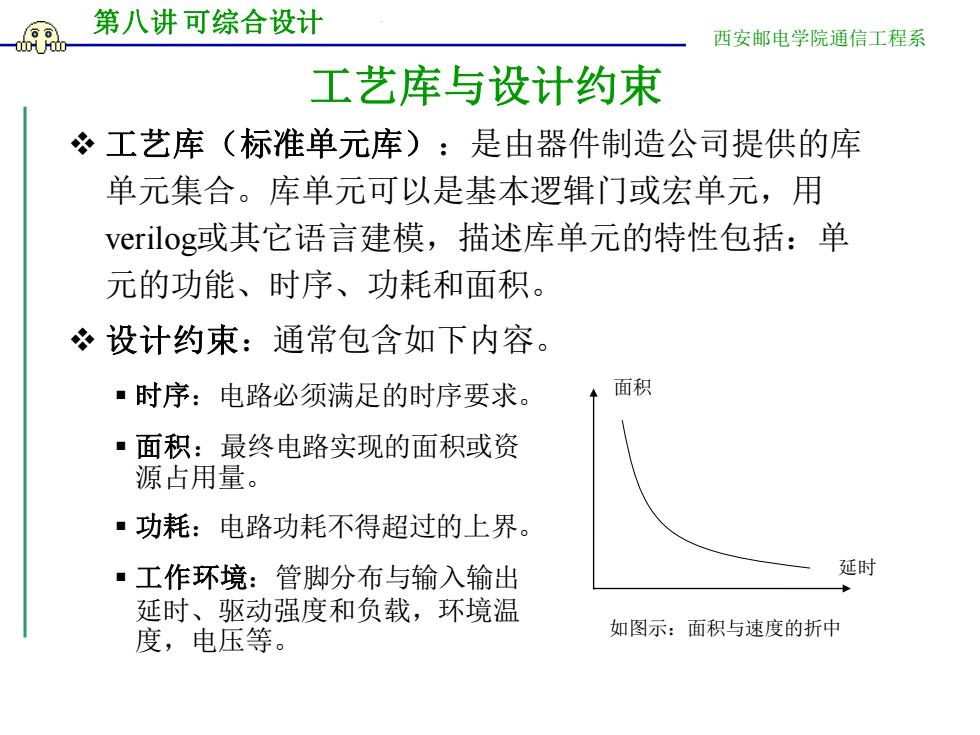

第八讲 可综合设计 西安邮电学院通信工程系 工艺库与设计约束 ❖ 工艺库(标准单元库):是由器件制造公司提供的库 单元集合。库单元可以是基本逻辑门或宏单元,用 verilog或其它语言建模,描述库单元的特性包括:单 元的功能、时序、功耗和面积。 ❖ 设计约束:通常包含如下内容。 ▪ 时序:电路必须满足的时序要求。 ▪ 面积:最终电路实现的面积或资 源占用量。 ▪ 功耗:电路功耗不得超过的上界。 ▪ 工作环境:管脚分布与输入输出 延时、驱动强度和负载,环境温 度,电压等。 延时 面积 如图示:面积与速度的折中

第八讲可综合设计 西安邮电学院通信工程系 逻辑综合实例 a3:0] 301 相等比较器: 3:U b3:0] 301 30 module compare(f,a,b); synplify综合的原理图 input [3:0]a,b; XOR2 b30 outputf reg f 30 always @(a or b) XOR2 OR2 NOR2 if (a ==b) f<=1b1; 2 fNE_2 f NE XOR2 else OR2 f<=1b0; fNE 1 endmodule XOR2 Synplify)用ACTEL的FPGA 工艺库综合的电路图

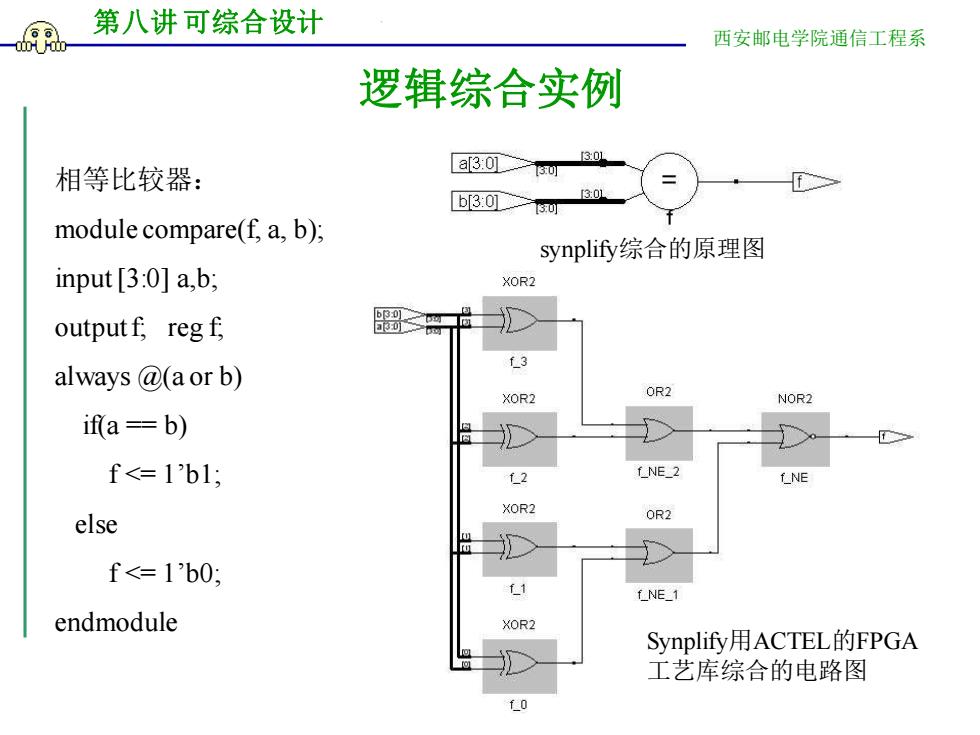

第八讲 可综合设计 西安邮电学院通信工程系 逻辑综合实例 相等比较器: module compare(f, a, b); input [3:0] a,b; output f; reg f; always @(a or b) if(a == b) f <= 1’b1; else f <= 1’b0; endmodule synplify综合的原理图 Synplify用ACTEL的FPGA 工艺库综合的电路图

第八讲可综合设计 西安邮电学院通信工程系 逻辑综合实例 b[3:01 a30 f_NE_a.G_2 f_NE_a.G_6_i_a2 Synplify用ALTERA的 FPGA工艺库综合的门 级电路图 NE_a.G_6_i_x2 f_0×G_2 f_NE.G_6 f_NE.G 4 a2416FF6 a2410009 b3:01 Synplify,用ALTERA的 a3:0]2 [3可 fNE FPGA工艺库综合的逻 f NE_a 辑单元映射电路图 a496666 fO_x

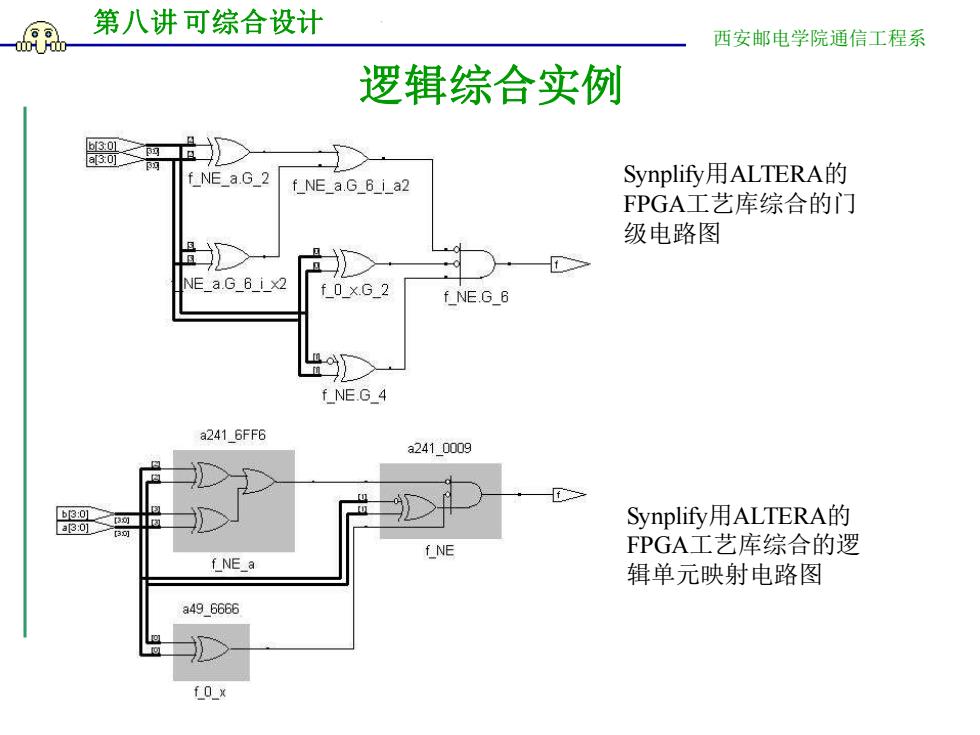

第八讲 可综合设计 西安邮电学院通信工程系 逻辑综合实例 Synplify用ALTERA的 FPGA工艺库综合的门 级电路图 Synplify用ALTERA的 FPGA工艺库综合的逻 辑单元映射电路图

第八讲可综合设计 西安邮电学院通信工程系 RTL级设计 RTL模型中的信号代表了硬件中数据的实际移动方向以及电路的 互连关系; 文 RTL模型中的语句与实际寄存器的结构模型之间存在直接的映射 关系; 必 RTL模型指定了寄存器级的电路元件之间的连接关系,但隐藏了 电路结构; 必 RTL模型指定了存储单元的复用结构及总线: 的 RTL模型中明确指定了各个寄存器的驱动时钟; RTL模型中通常不采用抽象的数据类型

第八讲 可综合设计 西安邮电学院通信工程系 RTL级设计 ❖ RTL模型中的信号代表了硬件中数据的实际移动方向以及电路的 互连关系; ❖ RTL模型中的语句与实际寄存器的结构模型之间存在直接的映射 关系; ❖ RTL模型指定了寄存器级的电路元件之间的连接关系,但隐藏了 电路结构; ❖ RTL模型指定了存储单元的复用结构及总线; ❖ RTL模型中明确指定了各个寄存器的驱动时钟; ❖ RTL模型中通常不采用抽象的数据类型

第八讲可综合设计 西安邮电学院通信工程系 RTL级可综合设计 Verilog可综合语句 函数function 不支持综合的Verilog语句 任务task 过程块 锁存器推断 寄存器 阻塞及非阻塞赋值 敏感列表 复位 持续赋值 资源共享 条件结构 复杂操作与宏库

第八讲 可综合设计 西安邮电学院通信工程系 RTL级可综合设计 • Verilog可综合语句 • 不支持综合的Verilog语句 • 过程块 • 寄存器 • 敏感列表 • 持续赋值 • 条件结构 • 函数function • 任务task • 锁存器推断 • 阻塞及非阻塞赋值 • 复位 • 资源共享 • 复杂操作与宏库