第七讲综合建模与仿真 西安邮电学院通信工程系 第七讲综合建模与仿真 内容: 常用模块建模(设计)实例 基于同步状态机的建模(设计) ÷存储器建模 冬仿真平台设计 冬仿真激励信号产生 冬功能仿真实例

第七讲 综合建模与仿真 西安邮电学院通信工程系 第七讲 综合建模与仿真 内容: ❖ 常用模块建模(设计)实例 ❖ 基于同步状态机的建模(设计) ❖ 存储器建模 ❖ 仿真平台设计 ❖ 仿真激励信号产生 ❖ 功能仿真实例

第七讲综合建模与仿真 西安邮电学院通信工程系 组合逻辑设计实例 在数字逻辑系统的设计中,从电路结构来看,基本上可 分为组合逻辑电路和时序逻辑电路两大类。 1.组合逻辑电路 组合逻辑电路的输出只与当时的输入信号有关, 而与 电路过去的状态无关,也即它的输出完全由输入信号和 输出函数决定。 在手工设计电路时期,组合逻辑主要设计优化工具是卡 若图,在目前EDA时期则是综合工具软件;设计者只需正 确描述电路功能,具体电路的优化由综合工具完成。 最常用的组合逻辑电路有编码器、译码器、数据选择 器、加法器和比较器等

第七讲 综合建模与仿真 西安邮电学院通信工程系 在数字逻辑系统的设计中,从电路结构来看, 基本上可 分为组合逻辑电路和时序逻辑电路两大类。 1. 组合逻辑电路 ❖ 组合逻辑电路的输出只与当时的输入信号有关, 而与 电路过去的状态无关, 也即它的输出完全由输入信号和 输出函数决定。 ❖ 在手工设计电路时期,组合逻辑主要设计优化工具是卡 若图,在目前EDA时期则是综合工具软件;设计者只需正 确描述电路功能,具体电路的优化由综合工具完成。 ❖ 最常用的组合逻辑电路有编码器、 译码器、 数据选择 器、 加法器和比较器等 。 组合逻辑设计实例

第七讲综合建模与仿真 西安邮电学院通信工程系 1)2/4译码器 选择字S,So 输 出 S:So D:D2 DD 2/4 0 0 0 0 01 D 01 0 0 10 10 0 1 00 D. 11 1 0 00 (a) (b) (a)符号;(b)功能表

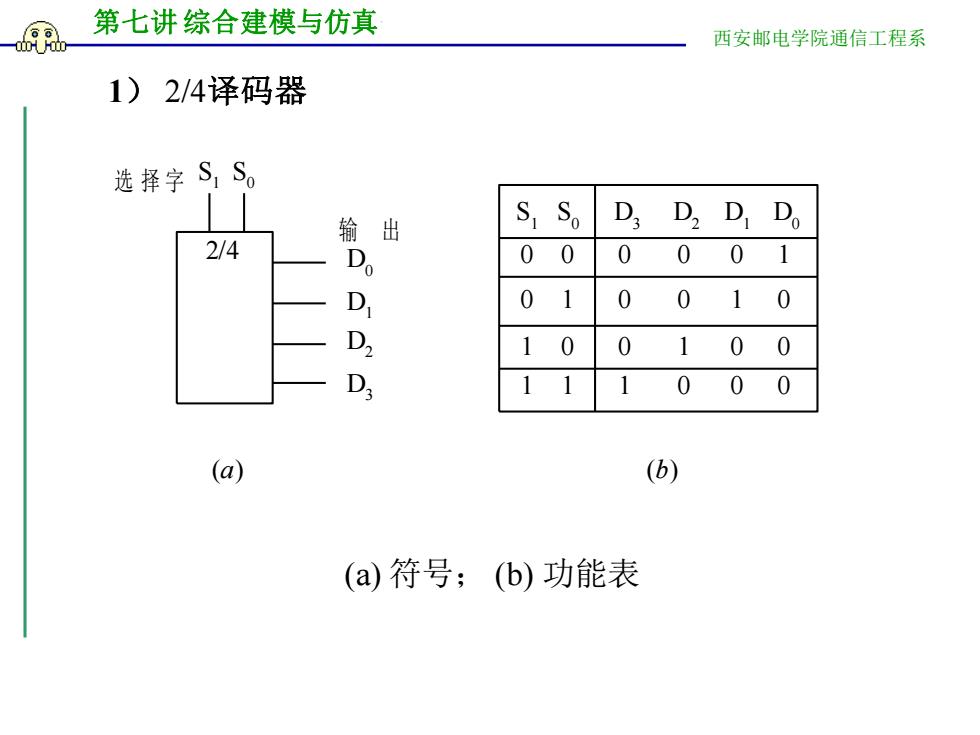

第七讲 综合建模与仿真 西安邮电学院通信工程系 (a) 符号; (b) 功能表 S1 S 选 择 字 0 输 出 D0 D1 D2 D3 (a) S1 S0 0 0 0 1 1 0 1 1 2/4 D3 0 0 0 1 D2 0 0 1 0 D1 0 1 0 0 D0 1 0 0 0 (b) 1) 2/4译码器

第七讲综合建模与仿真 西安邮电学院通信工程系 2/4译码器的功能描述1 module decode2 4(d,s); input [1:0]s, output [3:0]d; 条件S的选项要 完备,否则综 reg[3:0]d; 合工具将综合 出意外的锁存 always@(s)∥电平敏感变量表 器。 case(s) 2b00:d<=4b0001; 2b01:d<=4b0010; 2b10:d<=4b0100; 2b11:d<=4b1000; endcase 可用缺省default代 endmodule 替2b11

第七讲 综合建模与仿真 西安邮电学院通信工程系 2/4译码器的功能描述1 module decode2_4(d, s); input [1:0] s; output [3:0] d; reg[3:0] d; always @(s) //电平敏感变量表 case(s) 2’b00: d<=4’b0001; 2’b01: d<=4’b0010; 2’b10: d<=4’b0100; 2’b11: d<=4’b1000; endcase endmodule 条件S的选项要 完备,否则综 合工具将综合 出意外的锁存 器。 可用缺省default代 替 2‘b11

第七讲综合建模与仿真 西安邮电学院通信工程系 2/4译码器的功能描述2 module decode2 4(d,s); input [1:0]s; output [3:0]d;reg[3:0]d; always@(s)∥电平敏感变量表 if(s==2'b00) /if语句实现有优先级,条件要完备 d<=4b0001; else if(s=2b01)d<=4b0010:, else if(s=2'b10)d<=4b0100, else d<=4'b1000: endmodule

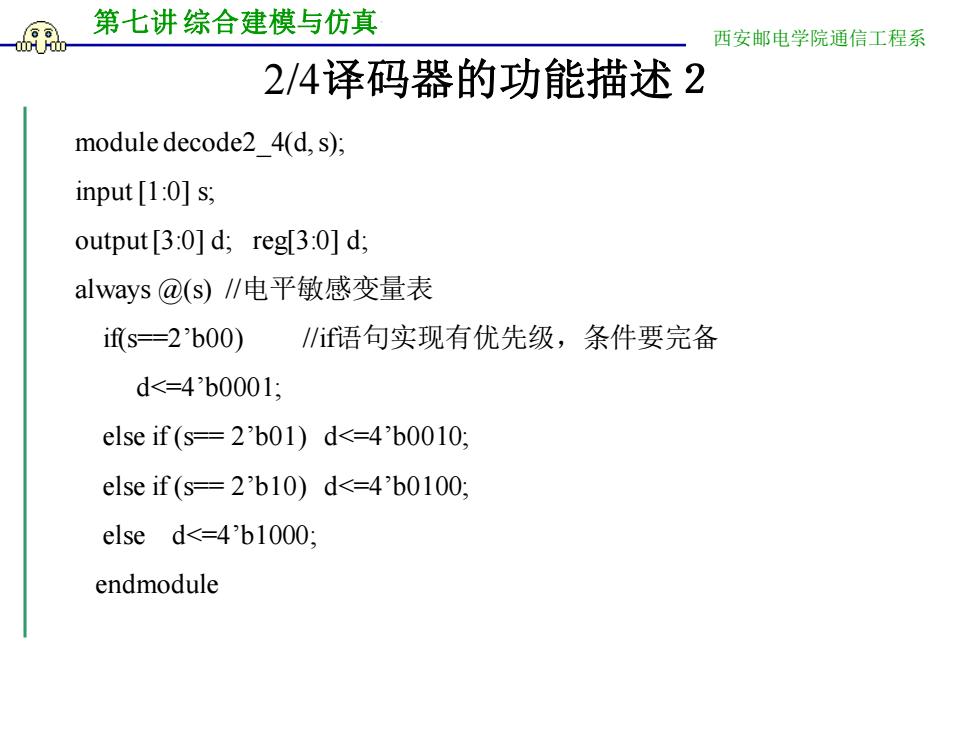

第七讲 综合建模与仿真 西安邮电学院通信工程系 2/4译码器的功能描述2 module decode2_4(d, s); input [1:0] s; output [3:0] d; reg[3:0] d; always @(s) //电平敏感变量表 if(s==2’b00) //if语句实现有优先级,条件要完备 d<=4’b0001; else if (s== 2’b01) d<=4’b0010; else if (s== 2’b10) d<=4’b0100; else d<=4’b1000; endmodule