第五讲行为建模 西安邮电学院通信工程系 第五讲行为建模1 内容: 行为建模 。过程块语句 ?过程赋值 冬过程中的块语句 过程的时序控制 冬阻塞与非阻塞过程赋值 ”条件语句

第五讲 行为建模 西安邮电学院通信工程系 第 五讲 行为建模1 内容: ❖ 行为建模 ❖ 过程块语句 ❖ 过程赋值 ❖ 过程中的块语句 ❖ 过程的时序控制 ❖ 阻塞与非阻塞过程赋值 ❖ 条件语句

第五讲行为建模 西安邮电学院通信工程系 行为建模(描述) 编译指令 模块定义 时序特性 Compiler directives module (port list) timig specifications 端口说明 数据类型说明 电路功能描述 子程序 Port declarations Data type declarations Circuit functionality subprograms 模块实例 输入 线网类型 任务 instantiation input net task 连续赋值 过程块 输出 寄存器类型 函数 Continuous Procedural function output register assignment blocks 双向 参数 赋值语句 过程块语句 系统任务和函数 inout parameter assign initial block System task always block function

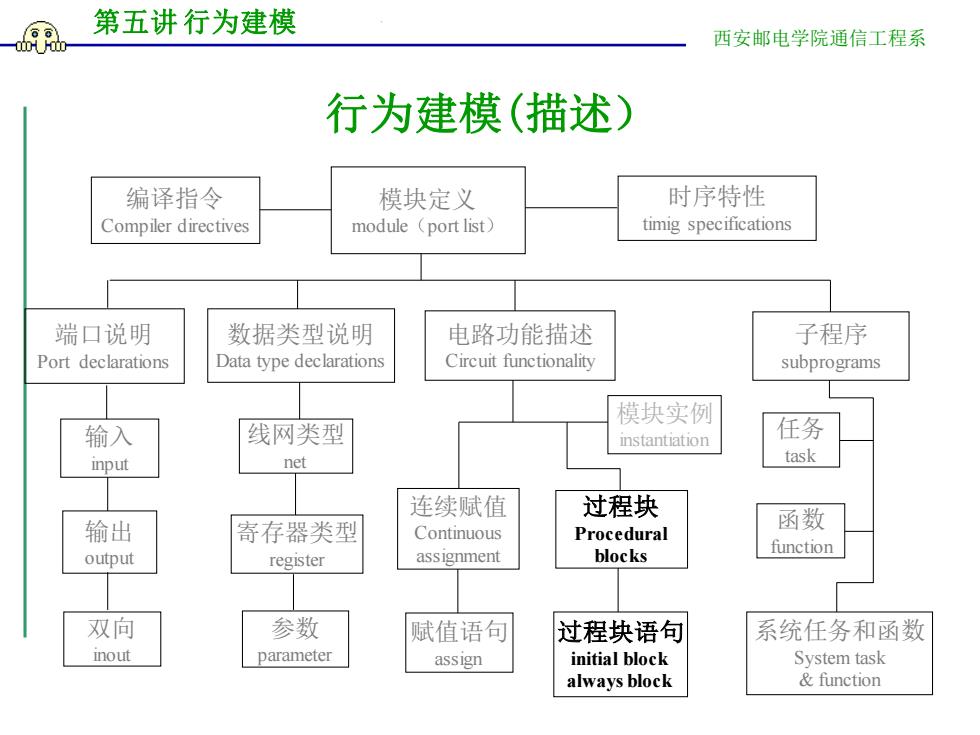

第五讲 行为建模 西安邮电学院通信工程系 行为建模(描述) 模块定义 module(port list) 时序特性 timig specifications 端口说明 Port declarations 输入 input 双向 inout 输出 output 数据类型说明 Data type declarations 线网类型 net 参数 parameter 寄存器类型 register 电路功能描述 Circuit functionality 子程序 subprograms 任务 task 函数 function 系统任务和函数 System task & function 编译指令 Compiler directives 连续赋值 Continuous assignment 赋值语句 assign 过程块 Procedural blocks 过程块语句 initial block always block 模块实例 instantiation

第五讲行为建模 西安邮电学院通信工程系 行为建模(描述) 行为级描述是对系统的高抽象级描述。在这个抽象级,注重的是整个系统的功能 而不是实现。 Verilog?有高级编程语言结构用于行为描述,包括:initial,always,@,wait, for,while,if else,case和forever等。 Veri1og的行为建模是用一系列以高级编程语言编写的并行的、动态的过程块来描 述系统的工作。 CIr D触发器行为 在每一个时钟上升沿, 若C1r不是低电平, 置Q为D值, Data 置Qb为D值的反 DFF Qb 无论何时C1r变低 置Q为0, Clk 置Qb为1

第五讲 行为建模 西安邮电学院通信工程系 行为建模(描述) ❖ 行为级描述是对系统的高抽象级描述。在这个抽象级,注重的是整个系统的功能 而不是实现。 ❖ Verilog有高级编程语言结构用于行为描述,包括:initial, always,@, wait, for, while, if else, case 和 forever 等。 ❖ Verilog的行为建模是用一系列以高级编程语言编写的并行的、动态的过程块来描 述系统的工作。 在每一个时钟上升沿, 若Clr不是低电平, 置Q为D值, 置Qb为D值的反 D触发器行为 无论何时Clr变低 置Q为0, 置Qb为1

第五讲行为建模 西安邮电学院通信工程系 过程块(procedural) 过程块是行为模型的基础。一个模块中可以有多个过程块,过程块有两种: ▣initial:块,只能执行一次 ▣always:块,循环执行 过程块中有下列部件 口过程赋值语句:描述过程块中的数据流 口时序控制:控制块的执行及块中的语句时序 口高级结构(循环,条件语句等):描述块的功能 initial always

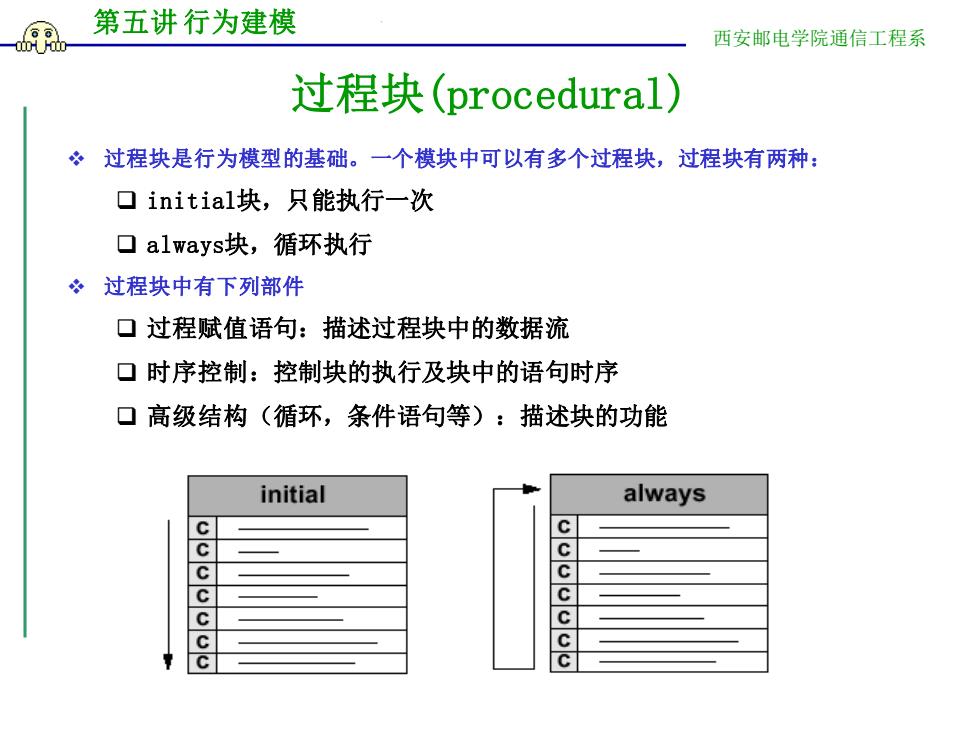

第五讲 行为建模 西安邮电学院通信工程系 过程块(procedural) ❖ 过程块是行为模型的基础。一个模块中可以有多个过程块,过程块有两种: ❑ initial块,只能执行一次 ❑ always块,循环执行 ❖ 过程块中有下列部件 ❑ 过程赋值语句:描述过程块中的数据流 ❑ 时序控制:控制块的执行及块中的语句时序 ❑ 高级结构(循环,条件语句等):描述块的功能

第五讲行为建模 000H 西安邮电学院通信工程系 过程块initial和always 冬都从0时刻开始执行; module name(.) input. ∥端口说明 initial无触发条件,只执 output . 行一次: reg . ∥信号说明 Always按触发条件执行,或 wire. ∥功能描述 无触发条件时一直执行; assign.∥并行赋值语句 冬一个module的行为描述中可 initial. ∥过程块语句 以有多个initial和always always.∥过程块语句 initial. 语句,即有多个过程块存在, assign. 且相互独立,并行运行。 always. endmodule

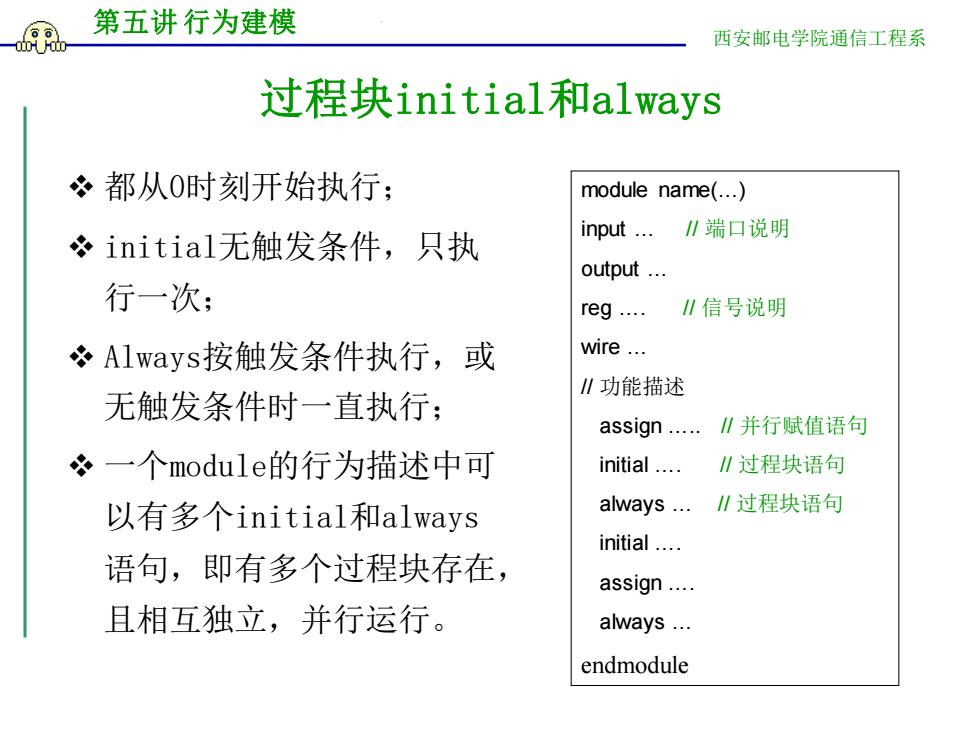

第五讲 行为建模 西安邮电学院通信工程系 过程块initial和always ❖ 都从0时刻开始执行; ❖ initial无触发条件,只执 行一次; ❖ Always按触发条件执行,或 无触发条件时一直执行; ❖ 一个module的行为描述中可 以有多个initial和always 语句,即有多个过程块存在, 且相互独立,并行运行。 module name(.) input . // 端口说明 output . reg . // 信号说明 wire . // 功能描述 assign . // 并行赋值语句 initial . // 过程块语句 always . // 过程块语句 initial . assign . always . endmodule