4.1组合逻辑电路分析 例2:电路如图所示,分析该电路的逻辑功能。 解:(1)由逻辑图逐级写出表达式 & P=ABC B L=AP+BP+CP AABC BABC +CABC (2)化简与变换: 真值表 L=ABC(A+B+C)=ABC+A+B+C ABC L 000 1 (3)由表达式列出真值表。 001 0 010 0 (4)分析逻辑功能: 011 0 100 0 当A、B、C三个变量一致时,输出为 101 0 “1”,所以这个电路称为”一致电路”。 110 0 111 1

例2:电路如图所示,分析该电路的逻辑功能。 解:(1)由逻辑图逐级写出表达式 (2)化简与变换: (3)由表达式列出真值表。 P = ABC L = AP+ BP +CP = AABC + BABC +CABC L = ABC(A+ B +C) (4)分析逻辑功能 : 当A、B、C三个变量一致时,输出为 “1” ,所以这个电路称为“一致电路” 。 = ABC + A+ B+C 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 A B C 1 0 0 0 0 0 0 1 L 真值表 & & & & A ≥1 B C L P 4.1组合逻辑电路分析

4.2常用组合逻辑电路的介绍 4.2.1加法器 l.半加器(Half Adder) 不考虑低位进位,将两个1位二进制数相加的逻辑运算 •半加器的真值表 ·逻辑表达式 S=AB+AB C=AB ·逻辑电路图 ·逻辑符号图 逻辑符号图

4.2常用组合逻辑电路的介绍 4.2.1加法器 不考虑低位进位,将两个1位二进制数相加的逻辑运算 • 半加器的真值表 • 逻辑表达式 • 逻辑电路图 1 0 0 0 C 1 1 0 0 1 1 1 0 1 0 0 0 A B S 半加器的真值表 S = AB+ AB C = AB A B =1 & C=AB S = A B 1.半加器(Half Adder) A B S C ∑ • 逻辑符号图 逻辑符号图

4.2常用组合逻辑电路的介绍 2.全加器(Full Adder) 全加器进行加数、被加数和低位来的进位信号的相加 全加器真值表 Ai 逻辑表达式 B S =ABC+4BCABC+4l Ci-1 =A⊕B,⊕C C,=A,B,+B,C,-1+A,C,- 逻辑符号图 逻辑电路图 ⊙西安邹重孝院

1 1 1 1 1 0 1 0 1 1 0 0 0 1 1 0 1 0 0 0 1 1 1 0 1 0 1 1 0 0 1 1 0 1 0 0 0 0 0 0 Ai Bi Ci-1 Si Ci 全加器真值表 全加器进行加数、被加数和低位来的进位信号的相加 2.全加器(Full Adder) 1 1 1 1 1 − − − − − = = + + + i i i i i i i i i i i i i i i i A B C S A BC A BC A BC A BC Ci = Ai Bi + Bi Ci−1 + Ai Ci−1 A i B i C i - 1 C i S ∑ i C I C O A i B i =1 & & & C i - 1 =1 S i C i 逻辑符号图 逻辑电路图 逻辑表达式 全加器真值表 4.2常用组合逻辑电路的介绍

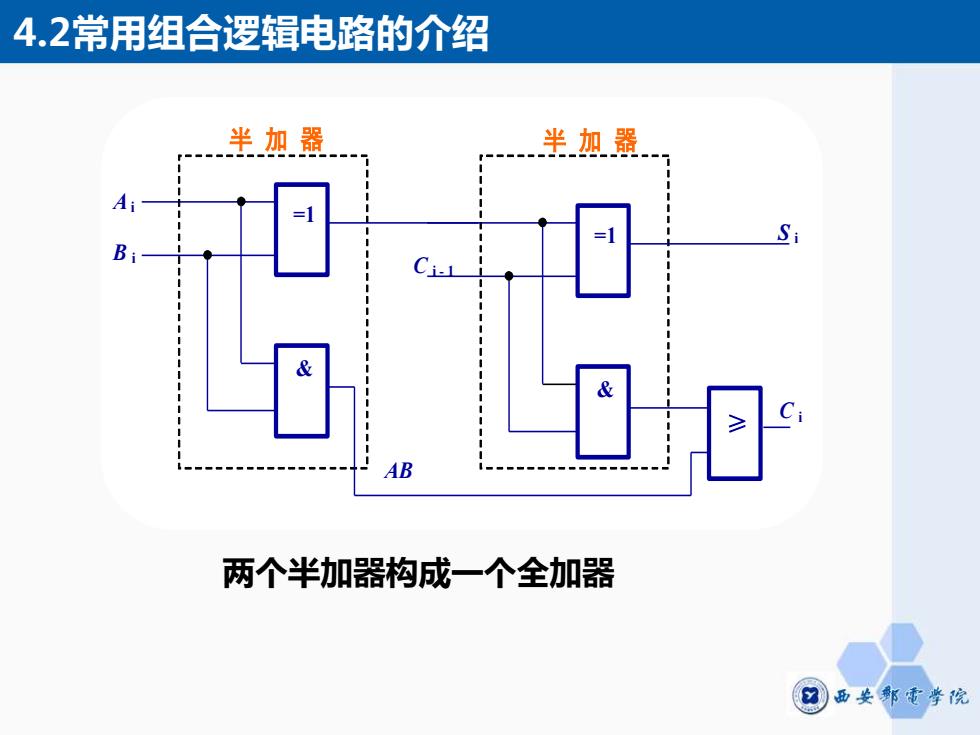

4.2常用组合逻辑电路的介绍 半加器 半加器 B 两个半加器构成一个全加器 ⊙西安邹重学院

A i B i =1 & AB C i - 1 =1 & ≥ 1 S i C i 半 加 器 半 加 器 两个半加器构成一个全加器 4.2常用组合逻辑电路的介绍

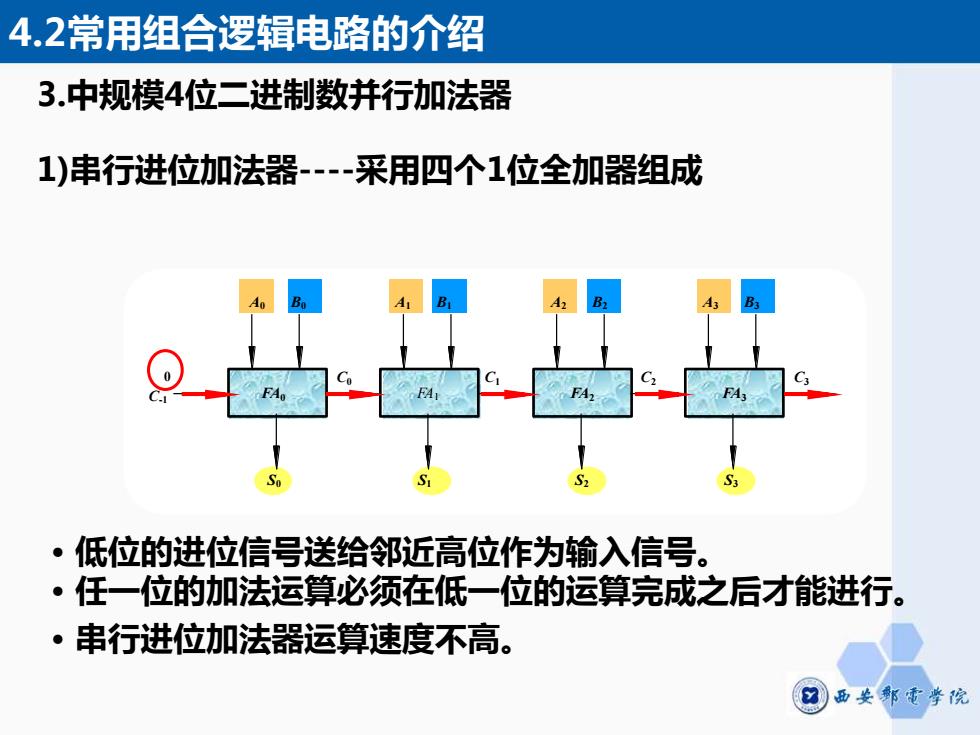

4.2常用组合逻辑电路的介绍 3.中规模4位二进制数并行加法器 1)串行进位加法器-采用四个1位全加器组成 ·低位的进位信号送给邻近高位作为输入信号。 ·任一位的加法运算必须在低一位的运算完成之后才能进行。 ·串行进位加法器运算速度不高

3.中规模4位二进制数并行加法器 1)串行进位加法器-采用四个1位全加器组成 A0 B0 A1 B1 A2 B2 A3 B3 S0 S1 S2 S3 C-1 0 C0 C1 C2 C3 FA0 FA1 FA2 FA3 • 低位的进位信号送给邻近高位作为输入信号。 • 任一位的加法运算必须在低一位的运算完成之后才能进行。 • 串行进位加法器运算速度不高。 4.2常用组合逻辑电路的介绍