口回☒ 日时g△品面B8必园五通日 1 ime:0.0ns End Time:1.0us Start Pause Stop Open SCF 图4-1-26仿真完成后的参数显示 单击“Open SCF”按钮,出现如图41-27所示波形图仿真结果 根据仿真结果,填写表41所示真值表,并求出逻辑函数表达式Y 表411 X 0 2000-300ns4000s5000ns6000ns70m06000ns9000%1 图41-27被形图编辑器仿真结果 (9)指定、设置CPLD芯片 单击菜单“Assign\Device.”出现如图4-1-28所示对话框,在对话框中需要制定下载所

单击“Open SCF”按钮,出现如图 4-1-27 所示波形图仿真结果。 根据仿真结果,填写表 4-1-1 所示真值表,并求出逻辑函数表达式 Y= 。 (9)指定、设置 CPLD 芯片 单击菜单“Assign\Device.”出现如图 4-1-28 所示对话框,在对话框中需要制定下载所

用的CPLD芯片。在本实验中选用的是“MAX7000S”系列的“EPM7032SLCC44-10”芯片, 注意选择前要把可选框“Show Only Fastest Speed Grades”前的对钩去掉。 Device ☒ Device Famly: 22tC4410 Auto Device. Migtalion Devic Edt Chips>> 图4-1-28指定CPLD芯片 单击菜单“△ssign\Global Project Device Options. 出现如图41-29所示对话框, 在对话框中设置所用的CPLD芯片。 C1 nasic AI G1 obal Project☒ oBns0x日 oge Cal0*目 User Code:FFFF [2-8te Hexedecimall 图4-1-29设置CPLD芯片 单击菜单“Assign\Global Project Logic Synthesis.”出现如图41-30所示对话框 设置CPLD芯片的模拟方式。在“Global Project Synthesis Style”选项中选择“FAST”, 其他可选框按照图4-130所示进行设置

用的 CPLD 芯片。在本实验中选用的是“MAX7000S”系列的“EPM7032SLCC44-10”芯片, 注意选择前要把可选框“Show Only Fastest Speed Grades”前的对钩去掉。 单击菜单“Assign\Global Project Device Options.”出现如图 4-1-29 所示对话框, 在对话框中设置所用的 CPLD 芯片。 单击菜单“Assign\Global Project Logic Synthesis.”出现如图 4-1-30 所示对话框, 设置 CPLD 芯片的模拟方式。在“Global Project Synthesis Style”选项中选择“FAST”, 其他可选框按照图 4-1-30 所示进行设置

Clobal Project Logic Synthesis ☒ EAST■ Beline Syrihesis Sye nS Machire Encoding 置Ax4 plus II-Compiler k☐ Cancel 宝□ 图4-1-30设置模拟方式 图4-1-31保存检查结果(10)管脚定位 单击图标图出现如图41-3引所示消息框,单击确定按钮,出现如图41-32所示编译器 窗口,单击START按钮开始编译,正确编译后出现如图4133单击确定按钮,编译过程完 成。 单击图标,然后再单击菜单“Layout evice View”,则出现如图434所示窗口。 口▣☒ Start 图41-32编译器窗口

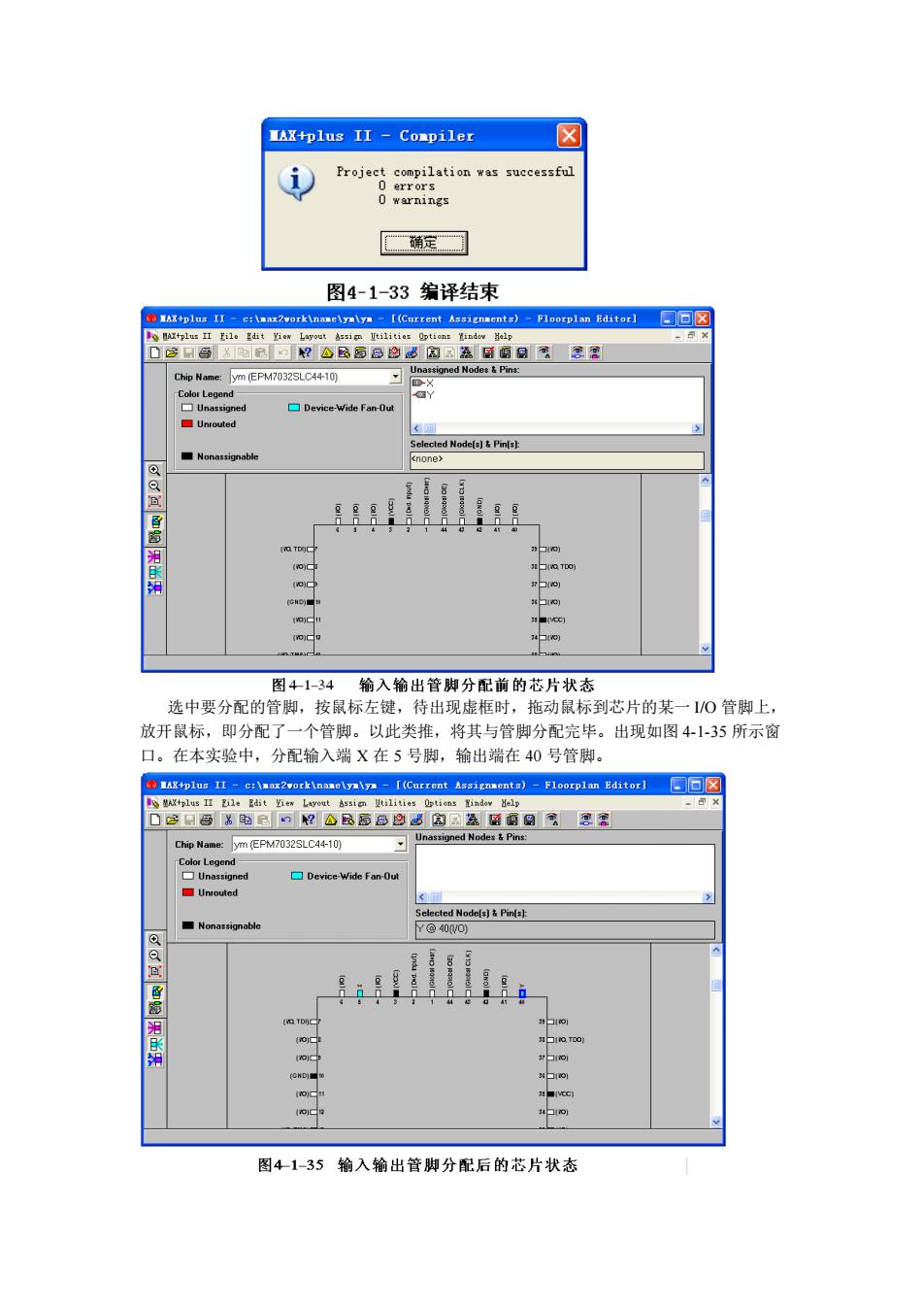

单击图标 出现如图 4-1-31 所示消息框,单击确定按钮,出现如图 4-1-32 所示编译器 窗口,单击 START 按钮开始编译,正确编译后出现如图 4-1-33 单击确定按钮,编译过程完 成。 单击图标 ,然后再单击菜单“Layout\Device View”,则出现如图 4-1-34 所示窗口。 若在“Unassigned Nodes & Pins”选项框中没有项目,则可单击窗口左侧有上自下的第 四个图标,将出现还未分配的输入/输出管脚

IAX+plus II -Compiler ☒ 定 图4-1-33编译结束 =mEPM7032SLC4410 口Device Wide Fan0u Node(s]Pinds) ■Na 图41- 输入输出管脚分配前的芯片状态 选中要分配的管脚,按鼠标左健,待出现虚框时,拖动鼠标到芯片的某一管脚上 放开鼠标,即分配了一个管脚。以此类推,将其与管脚分配完毕。出现如图4135所示窗 口。在本实验中,分配输入端X在5号脚,输出端在40号管脚。 Chip Name:ym (EPM7032SLC4410) □Device Wide Fan-Ou 图41-35输入输出管脚分配后的芯片状态

选中要分配的管脚,按鼠标左键,待出现虚框时,拖动鼠标到芯片的某一 I/O 管脚上, 放开鼠标,即分配了一个管脚。以此类推,将其与管脚分配完毕。出现如图 4-1-35 所示窗 口。在本实验中,分配输入端 X 在 5 号脚,输出端在 40 号管脚

单击图标雪对工程保存、编译,正确完成后,回到原理图编译器,可看到如图4-13 所示窗口。此时,CPLD管脚的分配结果已被标注在原理图的输入输出管脚上。接下来就 可以对CPLD进行下载测试了。 IAEtplus II c:\max2workknamelyslys [ym.gdt Graphic Editor] 石▣☒ D含BSXB包回?△国后B色山回回a图面但至蔬第my8 A7~ 图41-36管脚分配后的原理图 (11)模型生成 单击菜单“FileCreate Default Symbol'”,然后在单击菜单“EileEdit Symbol”出 现如图4137所示窗口。图中显示的即为本实验的最终模型,在此还可以对模型名称和管 脚内部名称重新编辑。这种模型以后可以直接进行调用,尤其是在模块化设计时更为重要。 ●X+plus I1-e\aax2 work\nanelay-【y.sn-Snbo.-回☒ SMX+plusEil。Edit View Element业tilities assic Options里indow Help ☐它日昌为的色口?△函面®巴山国回蒸厨面图 A 图4-1-41模型生成窗口 2.注意事项 管脚分配时要注意CPLD实验板上的开关和L发光二极管等输入输出变量同CPLD 芯片管脚的对应关系,保证一一对应

单击图标 对工程保存、编译,正确完成后,回到原理图编译器,可看到如图 4-1-36 所示窗口。此时,CPLD 管脚的分配结果已被标注在原理图的输入/输出管脚上。接下来就 可以对 CPLD 进行下载测试了。 (11)模型生成 单击菜单“File\Create Default Symbol”,然后在单击菜单“File\Edit Symbol”出 现如图 4-1-37 所示窗口。图中显示的即为本实验的最终模型,在此还可以对模型名称和管 脚内部名称重新编辑。这种模型以后可以直接进行调用,尤其是在模块化设计时更为重要。 2.注意事项 管脚分配时要注意 CPLD 实验板上的开关和 L 发光二极管等输入/输出变量同 CPLD 芯片管脚的对应关系,保证一一对应