7.1概述 读写周期:前后两次读或两次写之间所要求的最小时间间隔。 Read cyde READ Write cyde Read access Read access WRTE Write access Data valid DATA Da他written 存储器读写时序示意图

7.1 概述 读写周期:前后两次读或两次写之间所要求的最小时间间隔。 存储器读写时序示意图

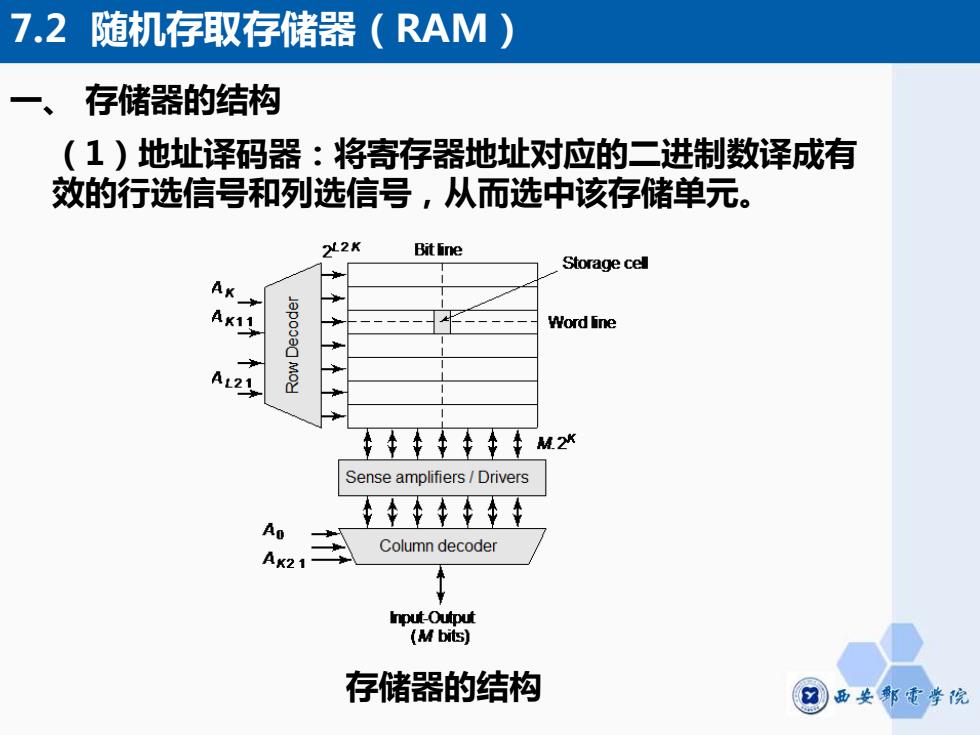

7.2 随机存取存储器(RAM) 存储器的结构 (1)地址译码器:将寄存器地址对应的二进制数译成有 效的行选信号和列选信号,从而选中该存储单元。 2L2K Bit line Storage cell AK AK11 Word iine 李↑专李卡M2* Sense amplifiers/Drivers Column decoder AK21 Iinput-Oulput (M bits) 存储器的结构 ⊙西邹重孝院

7.2 随机存取存储器(RAM) 一、 存储器的结构 (1)地址译码器:将寄存器地址对应的二进制数译成有 效的行选信号和列选信号,从而选中该存储单元。 存储器的结构

7.2 随机存取存储器(RAM) (2)存储单元 存储矩阵由许多存储单元排列组成,每个存储单元存 放一位二值信息。 水平选择线可以选择一行单元,称为字线(Wod Iine,也称为数据线),而把一列单元连接到输出电 路的线称为位线(bit line)。 (3)片选与读写控制电路 数字系统中的RAM一般要由多片组成,而系统每次读 /写时,只针对其中的一片或几片,因此还应加片选信 号 读/写控制信号用于对电路工作状态进行控制。 R/币=0时,执行写操作; R/W=1时,执行读操作

7.2 随机存取存储器(RAM) (2)存储单元 数字系统中的RAM一般要由多片组成,而系统每次读 /写时,只针对其中的一片或几片,因此还应加片选信 号 。 (3)片选与读写控制电路 水平选择线可以选择一行单元,称为字线(Word line,也称为数据线),而把一列单元连接到输出电 路的线称为位线(bit line)。 存储矩阵由许多存储单元排列组成,每个存储单元存 放一位二值信息。 读/写控制信号用于对电路工作状态进行控制。 R/W = 0 时,执行写操作; R/W =1 时,执行读操作

7.2 随机存取存储器(RAM) 二、静态随机存取存储器SRAM (1)SRAM存储单元 ①四管构成的SRAM存储单元 位线上的一对互为 反相信号可以通过 存储的数据也可 M3和M4向触发器 字线 以通过管子M3和 置数,也就是写入 M4向位线B和-B 过程。 VDD 传送,即所谓的 读出过程。 L23 M3 2 M4 GND -B 位线(数据线) 位线(数据线) SRAM4管存储单元结 构 ⊙西长郭重学院

7.2 随机存取存储器(RAM) 二、 静态随机存取存储器SRAM (1)SRAM存储单元 ① 四管构成的SRAM存储单元 L1 L2 VDD M3 M4 M1 M2 GND 位线(数据线) B 字线 位线(数据线) -B SRAM 4管存储单元结 构 位线上的一对互为 反相信号可以通过 M3和M4向触发器 置数,也就是写入 过程。 存储的数据也可 以通过管子M3和 M4向位线B和-B 传送,即所谓的 读出过程

7.2 随机存取存储器(RAM) ②六管构成的SRAM存储单元 解决了4T-SRAM存储单元的静态功耗问题。 CMOS结构提高了存储的可靠性和抗干扰能力。 M5 M6 两个反相器 M2 (M1,M5和 M2,M6构成两只 GND 反向器)组成的反 馈环路。 B -B 6T-SRAM CMOS 电路

7.2 随机存取存储器(RAM) ② 六管构成的SRAM存储单元 6T-SRAM CMOS 电路 GND B -B WL M1 M2 M3 M4 M5 M6 a b 两个反相器 (M1,M5和 M2,M6构成两只 反向器)组成的反 馈环路。 解决了4T-SRAM存储单元的静态功耗问题。 CMOS结构提高了存储的可靠性和抗干扰能力